# EC3353-ELECTRONIC DEVICES AND CIRCUITS UNIT-I PN JUNCTION DEVICES PART - B

## PN junction diode: structure, operation & V-I characteristics

With a neat diagram explain the working of a PN junction diode in forward bias And reverse bias and show the effects of temperature on its VI characteristics (NOV/DEC 2012), (May / June 2016), (Nov / Dec 2015)

(OR)

Outline the charge carrier diffusion phenomenon across a PN junction. Explain the effect of forward and reverse biasing on the depletion region. (Nov/Dec 2018 R-13) (April / May 2019-R17)

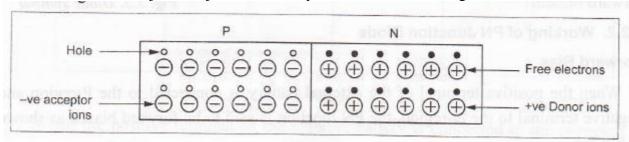

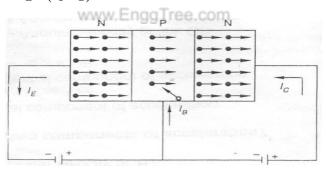

A **PN junction** is formed from a piece of semiconductor (Ge or Si) by diffusing p-type material (Acceptor impurity Atoms) to one half side and N type material to (Donar Impurity Atoms) other half side. The plane dividing the two zones is known as 'Junction'.

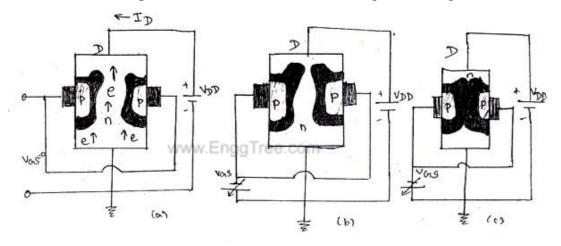

The P-region of the semiconductor contains a large number of holes and N region, contains a large number of electrons. A PN junction just immediately formed is shown in Fig.

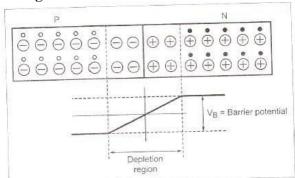

When PN junction is formed, there is a tendency for the electrons in the N-region to diffuse into the p-region, and holes from P-region to N-region. This process is called diffusion. While crossing the junction, the electrons and holes recombines with each other, leaving the immobile ions in the neighborhood of the junction neutralized as shown in Fig.

These immobile + ve and -ve ions, set up a potential across the junction. This potential is called potential barrier or junction barrier. Due to the potential barrier no further diffusion of electrons and holes takes place across the junction. Potential barrier is defined as a potential difference built up across the PN junction which restricts further movement of charge carriers across the junction. The potential barrier for a silicon PN junction is about 0.7 volt, whereas for Germanium PN junction is approximately 0.3 volt.

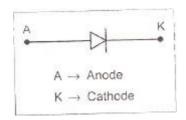

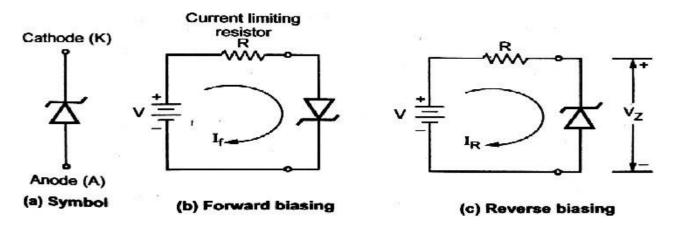

#### **Symbol of Diode:**

The symbol of PN junction diode is shown in Fig. The P-type and N-type regions are referred to as Anode and Cathode respectively. The arrowhead shows the conventional direction of current flow when the diode is forward biased.

## Working of PN Junction Diode:

#### **Forward Bias:**

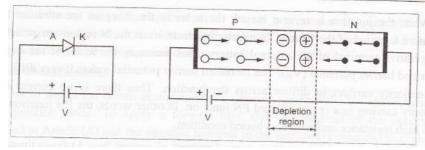

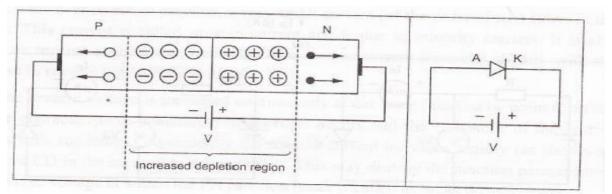

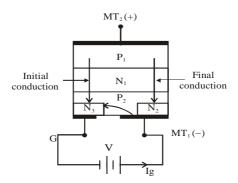

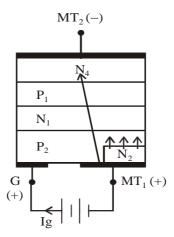

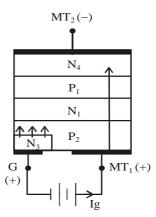

When the positive terminal of the external battery is connected to the P-region and negative terminal to the N-region, the PN junction is said to be forward biased as shown in Fig.

When the junction is forward biased, the holes in the p-region are repelled by the positive terminal of the battery and are forced to move towards the junction. similarly, the electrons in the N-region are repelled by the negative terminal of the battery and are forced to move towards the-junction.

This reduces the width of the depletion layer and barrier potential. If the applied voltage is greater than the potential barrier  $v_r$ , then the majority carriers namely holes in P-region and electrons in N-region, cross the barrier. During crossing some of the charges get neutralized the remaining charges after crossing, reach the other side and constitute current in the forward direction. The PN junction offers very low resistance under forward biased condition.

Since the barrier potential is very small (nearly 0.7 V for silicon and 0.3 V for Germanium junction), a small forward voltage is enough to completely eliminate the barrier. once the potential barrier is eliminated by the forward voltage, a large current start flowing through the PN junction.

#### **Reverse Bias:**

When the positive terminal of the external battery is connected to the N-region and negative terminal to the p-region, the PN junction is said to be reverse biased. When the junction is reverse biased, the holes in the P-region are attracted by the negative terminal of the battery. Similarly, the electrons in the N-region

are attracted by the positive terminal of the external battery. This increases the width of the depletion layer and barrier potential (Vs).

The increased barrier potential makes it very difficult for the majority carriers to diffuse across the junction. Thus, there is no current due to majority carriers in a reverse biased PN junction. In other words, the PN junction offers very high resistance under reverse biased condition.

In a reverse biased PN junction, a small amount of current (in  $\mu A$ ) flows through the junction because of minority carriers. (i.e., electrons in the P-region and holes in the N region). The reverse current is small because the number of majority carrier in both regions is small.

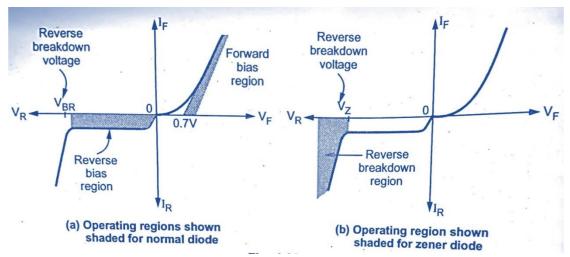

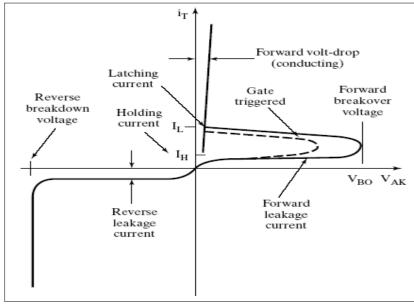

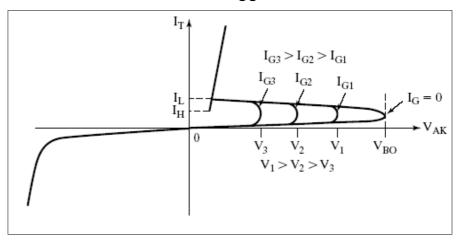

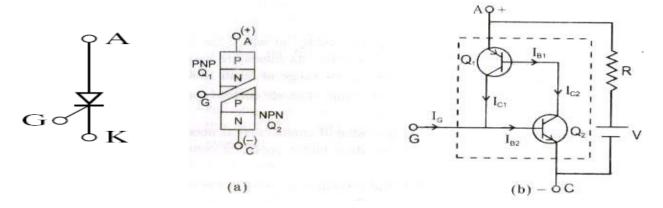

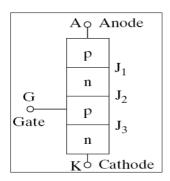

#### V-l characteristics of PN-Junction Diode:

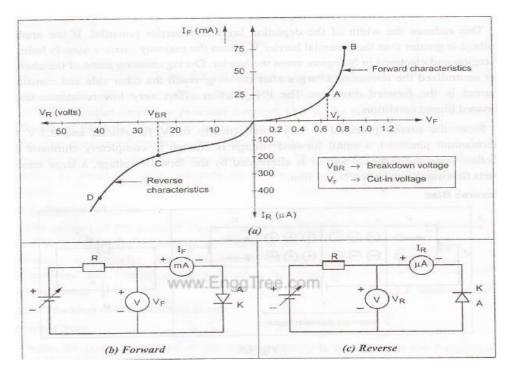

A graph between the voltage applied across the PN junction and the current flowing through the junction is called the V-I characteristics of PN junction diode. Fig. shows the V-I characteristics of PN junction diode.

#### **Forward Characteristics:**

Fig. (a) shows the circuit arrangement for drawing the forward V-I characteristics of PN junction diode. To apply a forward bias, the +ve terminal of the battery is connected to Anode (A) and the negative terminal of the battery is connected to Cathode (K). Now, when supply voltage is increased the circuit current increases very slowly and the curve is nonlinear (region-OA).

The slow rise in current in this region is because the external applied voltage is used to overcome the barrier potential (0.7 V for Si; 0.3V for Ge) of the PN junction' However once the potential barrier is eliminated and the external supply voltage is increased further, the current flowing through the PN junction diode increases rapidly (region AB). This region of the curve is almost linear. The applied voltage should not be increased beyond a certain safe limit, otherwise the diode will burnout.

The forward voltage at which the current through the PN junction starts increasing rapidly is called by **knee voltage**. It is denoted by the letter  $V_B$ .

#### **Reverse Characteristics:**

Fig (b) shows the circuit arrangement for drawing the reverse V-I characteristics of PN junction diode. To apply a reverse bias, the +ve terminal of the battery is connected to cathode (K) and - ve terminal of the battery is connected to anode (A).

Under this condition the potential buried at the junction is increased. Therefore, the junction resistance becomes very high and practically no. current flows through the circuit. However, in actual practice, a very small current (of the order of  $\mu A$ ) flows in the circuit. This current is called reverse current and is due to minority carriers. It is also called as reverse saturation current (I). The reverse current increases slightly with the increase in reverse bias supply voltage.

If the reverse voltage is increased continuously at one state (marked by point C on the reverse characteristics) breakdown of junction occurs and the resistance of the barrier regions falls suddenly. Consequently, the reverse current increases rapidly (as shown by the curve CD in the current) to a large value. This may destroy the junction permanently. The reverse voltage at which the PN junction breaks is called as break down voltage.

#### **Temperature effects**

The cut in voltage decreases as the temperature increases. The reverse saturation current increases.

$$I_{02} = 2^{(\Delta T/10)} I_{01}$$

$I_{01}$ , $I_{02}$  are the reverse current at  $T_1$ °C,  $T_2$ °C

$$\Delta T = T_2 - T_1$$

The voltage equivalent of temperature V<sub>T</sub> also increases. The reverse breakdown voltage increases.

#### 2. Derive the PN diode current equation.

The applied voltage and current though diode are related by the equation

$$I = I_0 \left( e^{V/yV_T} - 1 \right)$$

Where.

Io = Reverse saturation current

V = Applied voltage

I = Diode current

VT = Volt equivalent temperature

$$V_T = \frac{\overline{R}}{q}$$

$k = 1.38*10^{-23} \text{ J/K}$

T = temperature of the diode junction

I = diode current

$Q = \text{change of electron } 1.602*10^{-19} C$

At any temperature

$$V_T = \frac{R}{q} = \frac{1.38 \times 10^{-23}}{1.602 \times 10^{-19}} = \frac{T}{11600}$$

At room temperature

$$V_T = \frac{300}{11600} = 26mV$$

The value of  $\eta=1$  for germanium and 2 for silicon.

For forward bias voltage the current equation reduces to

$$I = I_0 \left( e^{V/yV_T} \right)$$

At room temperature for germanium transistor

$$I = I_0(e^{40})$$

When the diode is reverse biased

$$I=I_0\left(e^{V/yV_T}-1\right)$$

$$I \cong I_0$$

## **Diffusion and transient capacitance**

#### 3. Explain diffusion and transition capacitance of diode

Depletion layer capacitance (or) transition capacitance (or) space charge capacitance (May / June 2016)(Nov/Dec 2016)(May 2017)

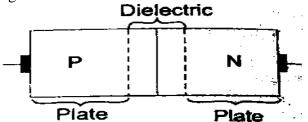

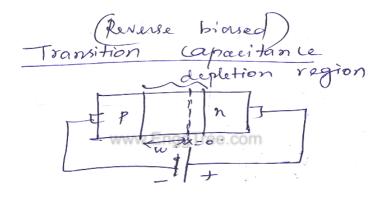

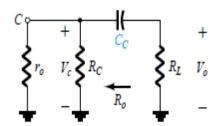

• When a PN junction is reverse biased, a layer of positive and negative immobile ions, called depletion layer, is formed on either side of the junction. It is also known as depletion-region, space-charge region or transition region. The depletion-layer acts as a dielectric (*i.e.*, non-conductive) medium between P-region and N-region. We know that the P-region and N-region on either side of the junction, has a low resistance. Therefore, these regions act as two plates of a capacitor, separated by a dielectric (*i.e.*, depletion layer) as shown in Fig.

The capacitance formed in a junction area is called depletion layer capacitance. It is also called depletion region-capacitance, space charge capacitance, transition region capacitance or simply junction capacitance.

- Since the depletion layer width (d) increases with the increase in reverse bias voltage, the resulting depletion layer capacitance will decrease with the increased reverse bias.

- The depletion layer capacitance depends upon the nature of a PN junction, semiconductor material and magnitude of the applied reverse voltage. It is given by the relation,

$$C_T = \frac{K}{(V_B - V)^n}$$

Where

K = A constant, depending upon the nature of semiconductor material

VB = barrier voltage. 0.6V for silicon and 0.3V for germanium

V = applied reverse voltage

n a constant depending upon the nature of junction.

The value of the K is

$$K = A \times \frac{\epsilon.q}{2} \left( \frac{N_A.N_D}{N_A + N_D} \right)$$

- The value of 'n' is taken as 1/2 for step or abrupt junction, 1/3 for linearly graded junction.

- It is the evident from the above relation that the value of depletion layer capacitance (CT) can be controlled by varying the applied reverse voltage. This property of variable capacitance, possessed by reverse biased PN junction, is used in the concentration of a device called varactor. Reverse biased.

#### **Derivation:**

Connection P side is less

Doping less in P side (NA)

N side (N<sub>D</sub>)

Potential & change density Relation

$${}^{N}_{A} < N_{D} \frac{d^{2}V}{dx^{2}} - \cdots - 1$$

$X-distance\ measured\ from\ junction$

$$N_{A} < N_{D} \frac{d2\sqrt[d]{\epsilon}}{dx^{2}} = \frac{qND}{s}$$

2

Integrating 2

$$\int \frac{d^2V}{dx^2} = \int \frac{qN_D}{\epsilon} \\ \frac{dv}{dx} = \frac{qN_AX}{\epsilon}$$

To get potential from 0 to w

$$\int_{o}^{V_{B}} \frac{dv}{dx} = \int_{o}^{w} \frac{q N_{A} X}{\epsilon} dx$$

Where V=VB

$$X=w$$

$$V_{B} = \frac{qN_{A}}{s} \times \frac{w^{2}}{2}$$

$$W = \sqrt{V_{B}}$$

3

Q=No of change particle  $\times$  change on each particle =(N<sub>A</sub>  $\times$  volume)  $\times$  q Q=qN<sub>A</sub>AW 2

Diff 3 w.r.to V

$$1 = \frac{qN_A}{s} \times \frac{1}{2} \frac{dw}{dv} 2w$$

Diff 2

$$V_B = \frac{qN_A}{\epsilon} \times \frac{w^2}{2}$$

$$\frac{dw}{dv} = \frac{\epsilon}{qN_Aw}$$

$$\frac{dQ}{dv} = qN_AA \frac{dw}{dv}$$

$$C_T = qN_AA \frac{\varepsilon}{aN_Aw} = \frac{A\varepsilon}{w}$$

$$C_T$$

Ex: Varactor diode (or) Tuning diode

www.EnggTree.com

## Diffusion capacitance C<sub>D</sub>:(May 2017)

The junction behaves like a capacitor. The capacitance, which exists in a forward-biased junction is called a *diffusion* or *storage capacitance*. It is different from the transition or depletion layer capacitance, which exists in a reverse-biased junction. The diffusion capacitance arises due to the arrangement of minority carrier density. And its value is much larger than the depletion layer capacitance.

Width of depletion region ↓ As applied voltage ↑, the concentration of injected charged particle also increases. This rate of change of injected change with applied voltage is capacitance.

r = mean lifetime of the carrier

I = value of forward current

$\eta = A$  constant (1 for Ge and 2 for Si)

V<sub>T</sub>=volt equivalent of temperature.

$$C_D = \frac{dQ}{dv}$$

$C_{Dis} > C_{T}$

$$I = I_{pn(0)} + I_{np(0)}$$

$I_{pn(0)} \rightarrow hole diffusion current n region$

$I_{np(0)} \rightarrow electron diffusion current in p region$

$$I_{np(0)} \simeq 0$$

P side heavily doped

$$J_{p(X)} = -qD_{p}\frac{dp_{n}}{dx}$$

$$J = \frac{I}{A}$$

$$\begin{split} I_p(X) &= -qAD_p \, \frac{dp_n}{dx} - 1 \\ P_n(X) &= P_{n(0)} e^{-X/LP} - 2 \end{split}$$

Hole concentration in the right side of p material  $P_{n(0)}$  ie junction Diff 2

$$\frac{dp_n(x)}{dx} = P_{n(0)} e_{-X/L^P} \left(\frac{1}{L_P}\right)$$

$$I_p(X) = -qAD_pP_{n(0)}e^{-X/LP}. -1/L_P$$

At  $x=0 I_p(X)=I_{pn(0)}=I$

$$I = \frac{QAD_P}{L_P} Pn (0)$$

www.EnggTree.com

$$Pn(0) = \frac{I L_P}{QAD_P} A$$

Now the excess minority charge exists only on n side and given by  $Q = \int_0^\infty Aq \, Pn(0) e^{-X/LP} dx$

$$= AqPn(0) \left[ \frac{e^{-X/L_p}}{\frac{-1}{L_p}} \right]^{\infty}$$

$$= AqLpPn(0) \left[ e^{-\infty} - e^{-0} \right]$$

$$=AqLpPn(0)[e^{-\infty} - e^{-0}]$$

$$Q=-AqLpPn(0)$$

Put A in B

$$Q = \frac{AqLpIL_P}{qADp} = \frac{L_P^2}{Dp}. I$$

Assume

$$\frac{{\rm L_P}^2}{{\rm Dp}} = r$$

$$\frac{L_{P}^{2}}{Dp} = r$$

$$Q=rI \Rightarrow \frac{dQ}{dI} = r$$

$$\begin{split} C_D &= \frac{dQ}{dI} \cdot \frac{dI}{dV} \\ C_D &= r. \frac{dI}{dV} \\ I &= I_o(e^{V/DVT}) \\ \frac{dI}{dV} &= I. \frac{1}{\eta V_T} \\ C_D &= r. \frac{I}{\eta V_T} \end{split}$$

It is evident from the above relation, that diffusion capacitance is directly proportional to the forward current (I).

## Rectifiers - Half Wave and Full Wave

#### Half Wave

## 4. What is halfwave rectifier? Explain the working principle with neat sketch? (Nov / Dec 2015) (Nov/Dec 2016)

Rectifiers are a class of circuits whose purpose is to convert ac waveforms (usually sinusoidal and with zero average value) into a waveform that has a significant non-zero average value (dc component). Simply stated, rectifiers are ac-to-dc energy converter circuits. Most rectifier circuits employ diodes as the principal elements in the energy conversion process; thus, the almost inseparable notions of diodes and rectifiers.

**Uncontrolled rectifier**: *uncontrolled* refers to the absence of any control signal necessary to operate the primary switching elements (diodes) in the rectifier circuit. (The discussion of controlled rectifier circuits, and the controlled switches themselves, is more appropriate in the context of power electronics applications). Rectifiers are the fundamental building block in dc power supplies of all types and in dc power transmission used by some electric utilities.

There are two types of rectifiers:

(a) Half Wave (HW) rectifier

(b) Full Wave (FW) rectifier

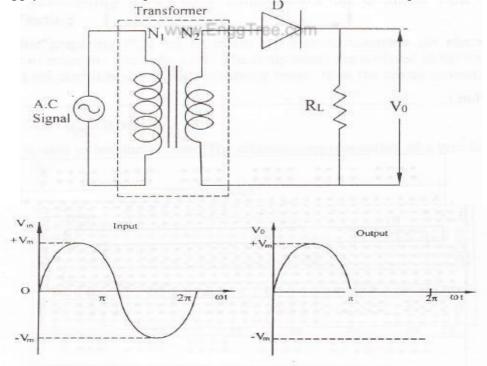

#### Half -wave Rectifier:

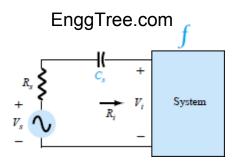

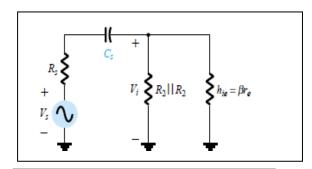

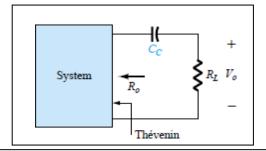

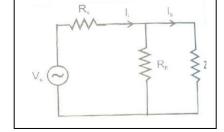

It consists of a single diode in series with a load resistor. The input to half wave rectifier is supplied from the 50 Hz a.c supply. The circuit diagram for halfwave rectifier is shown in fig.

#### Positive half cycle:

During the positive half cycle of the input signal the *anode of the diode becomes positive with respect to the cathode* and hence the diode D conducts. For an ideal to the cathode and hence the diode D conducts. For an ideal diode, the forward voltage drop is zero. So the whole-input voltage will appear across load resistance  $R_{\rm L}$ .

#### Negative half cycle:

During negative half cycle of the input signal, the anode of the diode becomes negative with respective to the cathode and hence the diode D does not contact. For an ideal diode the impedance by the diode is infinity. So the whole input voltage appears across the diode D. hence the voltage drop across R, is zero.

#### Analysis of Half wave rectifier:

Let Vi be the input voltage to the rectifier

$$V_i = V_m sin\omega t$$

Where,

$V_m = \text{Maximum value of the input voltage.}$

$$i = \{ \begin{cases} I_m sin\omega t & For \ 0 \le \omega t \le \pi \\ 0 & For \ \pi \le \omega t \le 2\pi \end{cases}$$

Where

$I_m = Maximum \ value \ of \ the \ current$

$$I_m = \frac{V_m}{R_F + R_L}$$

Where

$R_F$ -Forward dynamic resistance of diode.

R<sub>L</sub>-Load resistance.

#### (a) Average or DC value of output current (I<sub>dc</sub>):

From Fig., it is seen that the output current is not steady but contains fluctuations even though it is DC current. The average value of this fluctuating current is called DC current (I<sub>dc</sub>). It can be calculated as follows.

Average value = (Area under the curve / Period )

$$\begin{split} I_{dc} = & \frac{1}{2\pi} \int_0^{2\pi} i \ d(\omega t) \\ I_{dc} = & \frac{1}{2\pi} [\int_0^{\pi} I_m * \sin\omega t \ d(\omega t)] \\ I_{dc} = & \frac{1}{2\pi} [-\cos\omega t]_0^{\pi} = \frac{I_m}{2\pi} [-\cos\pi - (-\cos0)] = \frac{I_m}{2\pi} [-(-1) - (-1)] = \frac{I_m}{\pi} \\ I_{dc} = & \frac{V_m}{\pi (R_F + R_L)} \end{split}$$

(b) Average or DC output voltage  $(V_0)$ :

$$V_{dc} = \frac{I_m}{\pi} \times R_L = \frac{V_m}{\pi}$$

(c) RMS value of output current (I<sub>rms</sub>):

$$I_{rms} = \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} i^{2} d(\omega t) = \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} I_{m}^{2} \sin^{2}\omega t * d(\omega t) = \sqrt{\frac{I_{m}^{2}}{2\pi}} \int_{0}^{\pi} (\frac{1 - \cos 2\omega t}{2}) * d(\omega t)$$

$$= \sqrt{\frac{I_{m}^{2}}{4\pi}} \int_{0}^{\pi} d(\omega t) - \int_{0}^{\pi} \cos 2(\omega t) * d(\omega t) = \sqrt{\frac{I_{m}^{2}}{4\pi}} \left[\omega t_{0}^{\pi} - \left(\frac{\sin 2\omega t}{2}\right)^{\pi}\right]$$

$$= \sqrt{\frac{I_{m}^{2}}{4\pi}} \left[(\pi - 0) - \left(\frac{\sin 2\pi}{2} - \frac{\sin 0}{2}\right)\right] = \sqrt{\frac{I_{m}^{2}}{4\pi}} \left[(\pi - 0) - 0\right] = \sqrt{\frac{I_{m}^{2}}{4\pi}} = \frac{I_{m}}{2}$$

## (d) Rectification Efficiency (η):

Rectification efficiency (

$$\eta$$

) =  $\frac{I_{dc}^2 \times R_L}{I_{rms}^2 \times R_L}$  =  $\frac{\frac{I_m}{m^2} \times R}{\frac{I_m}{m^2} \times R}$  =  $\frac{I_m}{I_m} \frac{I_m}{m^2 \times R} = \frac{I_m}{I_m} \frac{I_m}{m^2 \times R} = \frac{I_m}{m^2} \frac{I_m}{m^2 \times R} = \frac{I_m}{m^2} \frac{I_m}{m^2} = 0.406$

#### (e) Ripple Factor ( $\gamma$ ):

$$y = \frac{I'}{I_{dc}} = \sqrt{\frac{I^2 - I^2}{I_{dc}^2}} = \sqrt{\frac{1}{(\frac{rms}{I_{dc}})^2} - 1} = \sqrt{\frac{I_{rms}/2}{I_{m/\pi}}}^2 - 1 = \sqrt{\frac{\pi^2}{4} - 1} = 1.21$$

#### (f) Peak inverse Voltage (PIV):

Peak inverse voltage is defined as the maximum voltage that is applied across the Diode when the diode is reverse biased. [n case of half wave rectifier, maximum Voltage across the diode when it is not conducting is equal to  $V_{\rm m}$ .

$$PIV = V_m$$

#### (g) From factor:

$$FF = \frac{rms\ value}{average\ value} = \frac{\pi}{2} = 1.57$$

#### (h) Peak factor:

$$PF = \frac{V_m}{(\frac{V_m}{2})} = 2$$

#### (i) Transformer utilization factor:

$$TUF = \frac{P_{dc}}{P_{ac}} (Transformer\ secondary\ rated) = 0.287$$

#### **Disadvantages of HWR:**

- ➤ Low output because one half cycle only delivers output

- A.C. component more in the output

- Requires heavy filter circuits to smooth out the output **Peak inverse Voltage.**

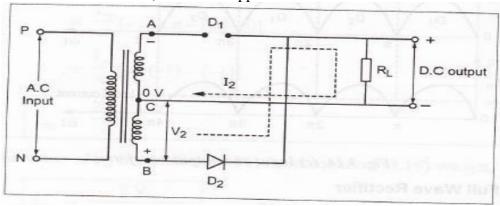

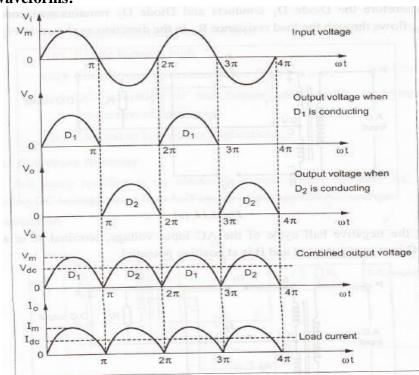

#### Rectifiers – Full Wave using center tap Transformer

- 5. Explain the operation of full wave rectifier with center tap transformer. Also derive the following for this rectifier. (Apr/May 2018)

- i) DC output voltage (average value) output voltage.

- ii) DC output current (average value) iii) RMS

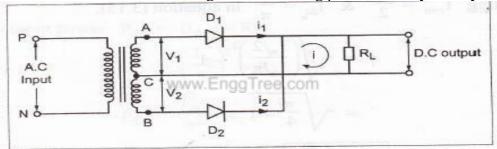

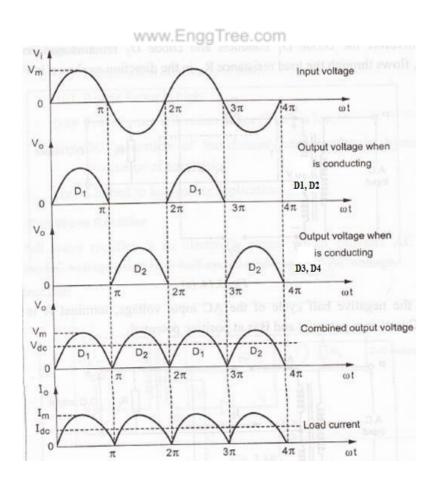

In FWR, current flows through the load during both half cycles of the input a.c. supply. Like the half wave circuit, a full wave rectifier circuit produces an output voltage or current which is purely DC or has some specified DC component. Full wave rectifiers have some fundamental advantages over their half wave rectifier counterparts. The average (DC) output voltage is higher than for half wave, the output of the full wave rectifier has much less ripple than that of the half wave rectifier producing a smoother output waveform.

#### **Full Wave Rectifier:**

A full wave rectifier is an electronic circuit which converts AC voltage into a pulsating DC voltage using both half cycles of the applied AC voltage. A full wave rectifier is a circuit which allows a unidirectional current to flow through the load during the entire input cycle as shown in fig. The result of full wave rectification is a d.c. output voltage that pulsates every half-cycle of the input. On the other hand a half wave rectifier allows the current to flow through the load during positive half-cycle only.

#### Positive half cycle:

The circuit uses two diodes which are connected to secondary winding of the transformer. The input signal is applied to the primary winding of the transformer. During the positive input half cycle, the polarities of the secondary voltage is shown in fig. This forward bias the diode D, and reverse biases the diode  $D_1$ . As a result of this, the diode D, conducts some current whereas the diode D, is off.

The current through load R1 is as indicated in through  $D_1$ , and the voltage Drop across  $R_L$  will the fig. The load current flows be equal to the input voltage.

#### **Negative half cycle:**

During the negative input half cycle, the polarities of the secondary voltage are interchanged. The reverse-bias the diode  $D_1$  and forward Biases the diode  $D_2$ . As a result of this, the diode  $D_1$  is OFF and the diode  $D_2$  conducts some current. The current through the load R, is an indicated in the fig. The load current flows through  $D_2$  and the voltage drop across  $R_1$  will be equal to the input voltage. The maximum efficiency of a fall-wave rectifier is 81,2%Vo and ripple factor is 0.48.

#### **Analysis of Full Wave Rectifier:**

Let Vi be the input voltage to the rectifier,  $V_i = V_m \sin \omega t$

Where,  $V_m = \text{Maximum value of the input voltage.}$

Let I be the current flowing though the circuit when the diode is conducting. Imsin $\omega t$  For  $0 \le \omega t \le \pi$

$$i = \{ \begin{cases} I_m sin\omega t & For \ 0 \le \omega t \le \pi \\ 0 & For \ \pi \le \omega t \le 2\pi \end{cases}$$

Where,  $I_m = Maximum \ value \ of \ the \ current;$   $I_m$

$$=\frac{V_m}{R_F+R_L}$$

Where,  $R_F$ -Forward dynamic resistance of diode;  $R_L$ -Load resistance.

#### Input and output waveforms:

#### (a) Average or DC value of output current ( Idc ):

Average value = (Area under the curve / Period)

$$\begin{split} I_{dc} &= \frac{1}{\pi} \int_0^{\pi} i \, d(\omega t) \\ I_{dc} &= \frac{1}{\pi} [\int_0^{\pi} I_m * \sin \omega t \, d(\omega t)] \\ I_{dc} &= \frac{1}{\pi} [-\cos \omega t]_0^{\pi} = \frac{I_m}{\pi} [-\cos \pi - (-\cos 0)] = \frac{I_m}{\pi} [-(-1) - (-1)] = \frac{2I_m}{\pi} \\ I_{dc} &= \frac{2V_m}{\pi (R_F + R_L)} \end{split}$$

#### (b) Average or DC value of output voltage ( $V_{dc}$ ):

$$V_{dc} = \frac{2I_m}{\pi} \times R_L = \frac{2V_m}{\pi}$$

#### (c) RMS value of output current (Irms):

$$I_{rms} = \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} i^{2} d(\omega t) = \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} I_{m}^{2} \sin^{2} \omega t * d(\omega t) = \sqrt{\frac{I_{m}^{2}}{\pi}} \int_{0}^{\pi} (\frac{1 - \cos 2\omega t}{2}) * d(\omega t)$$

$$= \sqrt{\frac{I_{m}^{2}}{2\pi}} \int_{0}^{\pi} d(\omega t) - \int_{0}^{\pi} \cos 2(\omega t) * d(\omega t) = \sqrt{\frac{I_{m}^{2}}{2\pi}} \left[\omega t^{\pi} - (\frac{\sin 2\omega t}{2})\right]^{\pi}$$

$$= \sqrt{\frac{I_{m}^{2}}{2\pi}} \left[(\pi - 0) - (\frac{\sin 2\pi}{2} - \frac{\sin 0}{2})\right] = \sqrt{\frac{I_{m}^{2}}{2\pi}} \left[(\pi - 0) - 0\right] = \sqrt{\frac{I_{m}^{2}}{2}} = \frac{I_{m}}{\sqrt{2}}$$

#### (d) Rectification Efficiency (η):

$$\text{Rectification efficiency ($\eta$)} = \frac{I_{dc}^2 \times R_L}{I_{rms}^2 \times R_L} = \frac{\frac{2I_m}{\pi}^2 \times R_L}{\frac{I_{lm}^2}{\sqrt{2}} \times R_L} = \frac{4I_m^2/\pi^2 \times R_L}{I_m^2/2 \times R_L} = \frac{0.812}{(1 + \frac{R_F}{L})} = 81.2\%$$

#### (e) Ripple Factor ( $\gamma$ ):

$$y = \frac{\text{RMS value of Ac component}}{\text{Dc value of wave}} = \sqrt{\left(\frac{\frac{\text{rms}}{\text{I}_{dc}}\right)^2 - 1} = \sqrt{\left(\frac{\frac{\text{I}}{\sqrt{2}}}{2\text{I}_{m}/\pi}\right)^2 - 1} = \sqrt{\frac{\pi^2}{8} - 1} = \mathbf{0}.\mathbf{48}$$

#### (f) Peak inverse Voltage (PIV):

Peak inverse voltage is the maximum possible voltage across a diode when it is not conducting. During positive half cycle of the AC input voltage Diode D1, is conducting and Diode D, is not conducting. In this case a voltage V, is developed across the load resistor  $R_1$ . Now the voltage across the non-conducting Diode D, is the sum of the voltage across  $R_1$  and voltage across the lower half of transformer secondary  $V_m$ .

Hence, PIV of Diode

$$D2 = V_m + V_m = 2V_m$$

Similary, PIV of Diode  $D1 = V_m + V_m = 2V_m$

#### **Advantages:**

- 1. The D.c load voltage and current are more than halfwave.

- 2. No D.c current thro transformer windings hence no possibility of saturation.

- 3. TUF is better.

- 4. Efficiency is higher.

- 5. Ripple factor less.

#### **Disadvantages:**

- 1. PIV rating of diode is higher

- 2. Higher PIV diodes are larger in size ad costlier.

- 3. Cost of transformer is high.

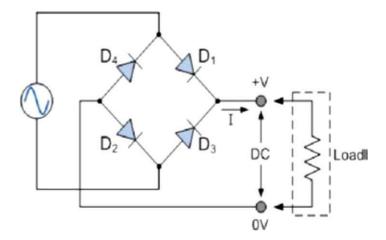

### Rectifiers – Full Wave Bridge type

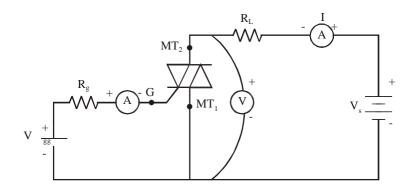

6. (a) Draw the circuit diagram and explain the working of full wave bridge rectifier & derive the expansion for average amount current & rectification efficiency. (May 2017) (Nov/Dec 2017) (Nov/Dec 2018)

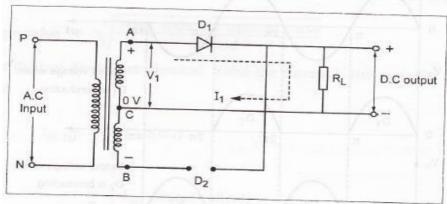

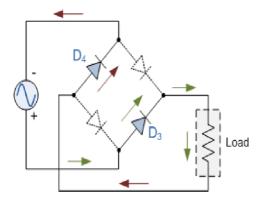

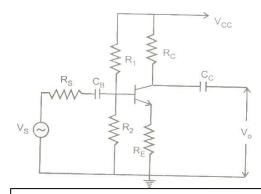

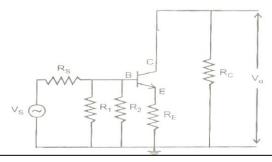

#### **Bridge rectifier (Full Wave Bridge rectifier):**

Another type of circuit that produces the same output waveform as the full wave rectifier circuit above is that of the **Full Wave Bridge Rectifier**. This type of single-phase rectifier uses four individual rectifying diodes connected in a closed loop "bridge" configuration to produce the desired output. The main advantage of this bridge circuit is that it does *not require a special center tapped transformer*, thereby reducing its size and cost. The single secondary winding is connected to one side of the diode bridge network and the load to the other side as shown below.

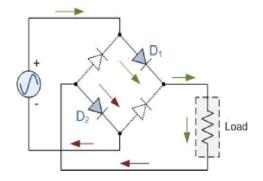

The four diodes labeled D1 to D4 are arranged in "series pairs" with only two diodes conducting current during each half cycle. *During the positive half cycle of the supply, diodes D1 and D2 conduct* in series while diodes D3 and D4 are reverse biased and the current flows through the load as shown below.

During the negative half cycle of the supply, diodes D3 and D4 conduct in series, but diodes D1 and D2 switch of as they are now reverse biased. The current flowing through the load is the same direction as before. As the current flowing through the load is unidirectional, so the voltage developed across the load is also unidirectional the same as for the previous two diode full-wave rectifier.

Positive half cycle

**Negative half cycle**

## Waveform:

#### **Analysis of Full Wave Rectifier:**

Let Vi be the input voltage to the rectifier,  $V_i = V_m sin\omega t$ Where.

$V_m$  = Maximum value of the input voltage.

Let I be the current flowing though the circuit when the diode is conducting.  $\lim_{I \to \infty} i = \{ 0 \quad For \ \pi \leq \omega t \leq 2\pi \}$

$$i = \{ \begin{cases} I_m \sin \omega t & For \ 0 \le \omega t \le \pi \\ 0 & For \ \pi \le \omega t \le 2\pi \end{cases}$$

Where

$$I_m = Maximum \ value \ of \ the \ current$$

$$I_m = \frac{V_m}{R_F + R_L}$$

Where,  $R_F$ -Forward dynamic resistance of diode;  $R_L$ -Load resistance.

### (a) Average or DC value of output current ( Idc ):

Average value = (Area under the curve / Period)

$$\begin{split} I_{dc} &= \frac{1}{\pi} \int_0^\pi i \, d(\omega t) & I_{dc} &= \frac{1}{\pi} [\int_0^\pi I_m * sin\omega t \, d(\omega t)] \\ I_{dc} &= \frac{1}{\pi} [-cos\omega t]_0^\pi = \frac{I_m}{\pi} [-cos\pi - (-cos0)] = \frac{I_m}{\pi} [-(-1) - (-1)] = \frac{2I_m}{\pi} \\ I_{dc} &= \frac{2V_m}{\pi (R_F + R_L)} \end{split}$$

## (b) Average or DC value of output voltage ( $V_{dc}$ ): $V_{dc} = \frac{2I_m}{\pi} \times R_L = \frac{2V_m}{\pi}$

## (c) RMS value of output current (I<sub>rms</sub>):

$$I_{rms} = \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} i^{2}d(\omega t) = \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} I_{m}^{2} \sin^{2}\omega t * d(\omega t) = \sqrt{\frac{I_{m}^{2}}{\pi}} \int_{0}^{\pi} (\frac{1 - \cos 2\omega t}{2}) * d(\omega t)$$

$$= \sqrt{\frac{I_{m}^{2}}{2\pi}} \int_{0}^{\pi} d(\omega t) - \int_{0}^{\pi} \cos 2(\omega t) * d(\omega t) = \sqrt{\frac{I_{m}^{2}}{2\pi}} [\omega t_{0}^{\pi} - (\frac{\sin 2\omega t}{2})]$$

$$= \sqrt{\frac{I_{m}^{2}}{2\pi}} [(\pi - 0) - (\frac{\sin 2\pi}{2} - \frac{\sin 0}{2})] = \sqrt{\frac{I_{m}^{2}}{2\pi}} [(\pi - 0) - 0] = \sqrt{\frac{I_{m}^{2}}{2}} \frac{I_{m}}{\sqrt{2}}$$

#### (d) Rectification Efficiency (η):

Rectification efficiency (

$$\eta$$

) =  $\frac{I_{dc}^2 \times R_L}{I_{rms}^2 \times R_L} = \frac{\frac{2I_m^2}{\pi}^2 \times R_L}{\frac{I_m^2}{\sqrt{2}} \times R_L} = \frac{4I_m^2/\pi^2 \times R_L}{I_m^2/2 \times R_L} = \frac{0.812}{(1 + \frac{R_F}{1})} = 81.2\%$

(e) Ripple Factor  $(\gamma)$ :

$$y = \frac{\text{RMS value of Ac component}}{\text{Dc value of wave}} = \sqrt{\left(\frac{\frac{1}{\text{rms}}}{I_{dc}}\right)^2 - 1} = \sqrt{\left(\frac{\frac{1}{m}}{2I_m/\pi}\right)^2 - 1} = \sqrt{\frac{\pi^2}{8} - 1} = \mathbf{0.48}$$

#### (f) Peak inverse Voltage (PlV):

Peak inverse voltage is the maximum possible voltage across a diode when it is not

Conducting. During positive half cycle of the AC input voltage Diode D1, is conducting and Diode D, is not conducting. In this case a voltage V, is developed across the load resistor  $R_1$ . Now the voltage across the non-conducting Diode D, is the sum of the voltage across  $R_1$  and voltage across the lower half of transformer secondary  $V_m$ .

Hence, PIV of Diode  $D2 = V_m + V_m = 2V_m$ Similary, PIV of Diode  $D1 = V_m + V_m = 2V_m$

#### Advantages:

- 1. The D.c load voltage and current are more than half wave.

- 2. No D.c current thro transformer windings hence no possibility of saturation.

- 3. TUF is better.

- 4. Efficiency is higher.

- 5. Ripple factor less.

- 6. No centre tapped is required.

#### **Disadvantages:**

4 diodes are used therefore voltage drop across the diode is increased. This reduces output voltage.

#### **Applications:**

- 1. In power supply circuits.

- 2. Used as rectifier in power circuits to convert A.C to D.C

- (b) In a bridge rectifier circuit, input supply is 230V, 50 Hz. Primary to secondary turns ratio is 4:1, load resistance is 200  $\Omega$ . The diodes are ideal. Find DC output voltage, PIV and output signal frequency. (Nov / Dec 2018-R17)

voltage, PIV and output signal frequency. (Nov / Dec 2018-R17) Solution:

$$E_{py}(rms) = 230V, \frac{N_2}{N_1} = \frac{1}{4}, R_L = 200\Omega$$

$R_f = R_s = 0\Omega$  as ideal

$$\frac{E_{py}(rms)}{E_{sy}(rms)} = \frac{N_1}{N_2}, E_{sy}(rms) = \frac{N_1}{N_2} X E_{py}(rms) = \frac{1}{4} X 230 = 57.5 V,$$

$$E_{sy\ (max)} = \sqrt{2\ E_{py\ (rms)}} = \sqrt{2\ X}\ 57.5 = 81.31\ V$$

$$I_{m} = \frac{E_{sm}}{R_{s} + 2R_{f} + R_{L}} = \frac{81.31}{200} = 0.4065 A_{DC} = \frac{2 I_{m}}{\pi} = \frac{2 \times 0.4065}{\pi} = 0.2587 A$$

$$E_{DC} = I_{DC} R_L = 0.2587 X 200 = 51.74 V$$

$$PIV = E_{sm} = 81.31V$$

(for full wave rectifier)

Output signal frequency =  $2f_s = 2 \times 50 = 100$ Hz

Ripple Factor (for Full Bridge Rectifier) = 0.482,

Ripple Factor =

$$\frac{AC \ rms \ output}{DC \ output} = \frac{Ripple \ Voltage}{E_{DC}}$$

0.482 =  $\frac{Ripple \ Voltage}{51.74}$

i.e. Ripple voltage =  $51.74 \times 0.482 = 24.94 \text{ V}$

#### 7. Compare different types of rectifiers?

| Type                | HW            | CT FW        | FW BR         |

|---------------------|---------------|--------------|---------------|

| No of diodes used   | 1             | 2            | 4             |

| Need of transformer | Not necessary | Necessary    | Not necessary |

| Ripple factor       | 1.21          | 0.48         | 0.48          |

| Efficiency          | 40.6%         | 81.2%        | 81.2%         |

| PIV                 | $V_{\rm m}$   | $2V_{\rm m}$ | $V_{\rm m}$   |

| TUF                 | 0.287         | 0.812        | 0.693         |

| From factor         | 1.57          | 1.11         | 1.11          |

| Peak factor         | 2             | $\sqrt{2}$   | $\sqrt{2}$    |

| Ripple frequency    | f             | 2f           | 2f            |

#### Display devices- LED

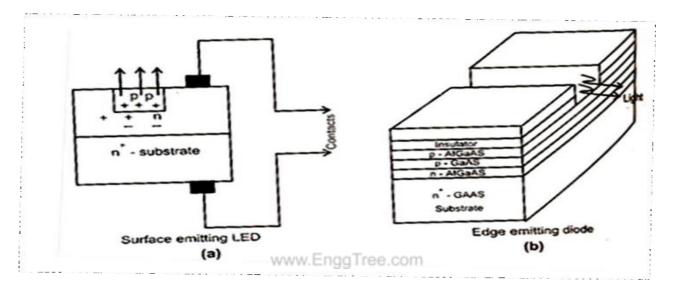

8. Discuss the working principle, characteristics and application of LED in detail. (NOV/DEC 2012) (Apr/May 2018)

Explain the principle and operation of light emitting diode (LED) with necessary expressions for current densities and efficiency of light generation. (April / May 2019-R17)

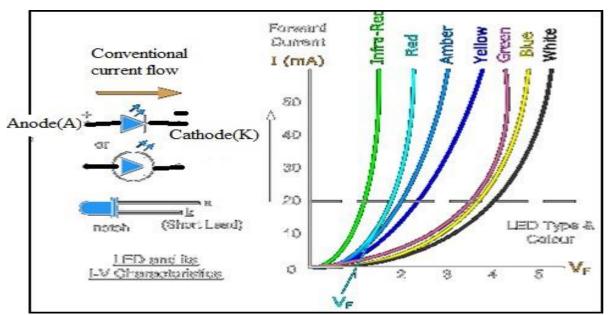

A **light-emitting diode**(LED) is a semiconductor light source LEDs are used as indicator lamps in many devices and are increasingly used for other lighting. Introduced as a practical electronic component in 1962, early LEDs emitted low-intensity red light, but modern versions are available across the visible, ultraviolet, and infrared wavelengths, with very high brightness.

When a light-emitting diode is forward-biased (switched on), electrons are able to recombine with electron holes within the device, releasing energy in the form of photons. This effect is called electroluminescence and the color of the light (corresponding to the energy of the photon) is determined by the energy gap of the semiconductor.

LEDs are often small in area (less than 1 mm<sup>2</sup>), and integrated optical components may be used to shape its radiation pattern.<sup>[5]</sup> LEDs present many advantages over incandescent light sources including lower energy consumption, longer lifetime, improved robustness, smaller size, and faster switching. LEDs powerful enough for room lighting are relatively expensive and require more precise current and heat management than compact fluorescent lamp sources of comparable output.

**Light Emitting Diodes** are made from exotic semiconductor compounds such as Gallium Arsenide (GaAs), Gallium Phosphide (GaP), Gallium Arsenide Phosphide (GaAsP), Silicon Carbide (SiC) or Gallium Indium Nitride (GaInN) all mixed together at different ratios to produce a distinct wavelength of colour.

Different LED compounds emit light in specific regions of the visible light spectrum and therefore produce different intensity levels.

- Gallium Arsenide Phosphide (GaAsP) red to infra-red, orange

- Aluminium Gallium Arsenide Phosphide (AlGaAsP) high-brightness red, orange-red, orange, and yellow

- Gallium Phosphide (GaP) red, yellow and green

- Aluminium Gallium Phosphide (AlGaP) green

- Gallium Nitride (GaN) green, emerald green

- Gallium Indium Nitride (GaInN) near ultraviolet, bluish-green and blue

- Silicon Carbide (SiC) blue as a substrate

- Zinc Selenide (ZnSe) blue

- Aluminium Gallium Nitride (AlGaN) ultraviolet

Light-emitting diodes are used in **applications** as diverse as aviation lighting, automotive lighting, advertising, general lighting, and traffic signals. LEDs have allowed new text, video displays, live video, and sensors to be developed, while their high switching rates are also useful in advanced communications technology. Infrared LEDs are also used in the remote control units of many commercial products including televisions, DVD players, and other domestic appliances.

## Laser diodes

#### 9. Explain in detail about LASER DIODE? (May / June 2016) (April/May 2018)

The term laser comes from the acronym for light amplification for stimulated emission of radiation. The laser medium can be a gas, liquid, amorphous solid or semiconductor.

#### **Laser Action**

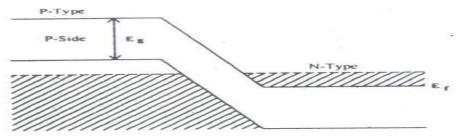

The light travelling through a semiconductor, then a single photon is able to generate an identical second photon. This photon multiplication is the key physical mechanism of lasing. The carrier inversion is the first requirement of lasing. It is achieved at the PN junction by providing the conduction bandwith electrons from the N-doped side and the valence band with holes from the P-doped side as shown in Fig. The photon energy is given by the band gap, which depends on the semiconductor material. The optical feedback and the confinement of photon in an optical resonator are the second basic requirement of lasing.

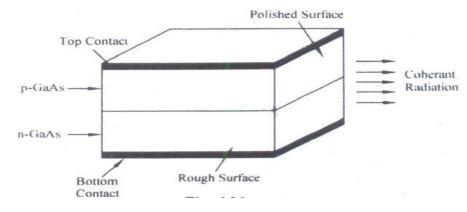

#### **PN Homojunction Laser**

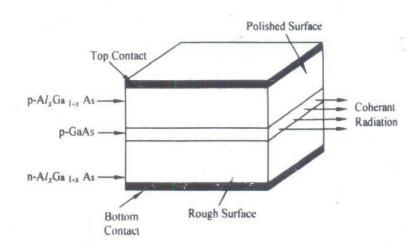

It has the material GaAs on both sides of the junction. A pair of parallel planes perpendicular to the plane of the junction are cleared and polished under appropriate biasing in off condition, laser light is emitted from these planes. The other two sides are deliberately roughened to prevent lasing in those directions. Such a cavity is called a Fabryperot resonant cavity with a typical cavity length of 300 |**J**.m. It is a thin layer of material with a narrow band gap. GaAs is sandwiched between layers of a material with band gap. This is usually realized by epitaxy. In such a structure the carrier are better confined in the active region due to the heterojunction barriers. Optical confinement is also better in **DH** laser. The propagation of the electromagnetic radiation is confined in a direction parallel to the

layer interface. The current density required for lasing in lower for *DH* lasers compared to homojunction lasers. The double preferred for continuous operation at room temperature.

Double Hetrostructure Laser

www.EnggTree.com

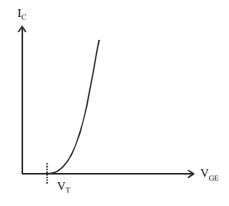

#### **Characteristics of Laser Diode**

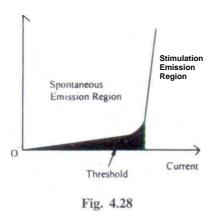

The Ideal light output against current characteristics for semiconductor laser is shown in Fig.4.28. The solid line represents the laser characteristics. It may be observed that the device gives low light output in the region, the threshold with corresponds to spontaneous emission only within the structure. After the threshold current value the light output increases substantially for small increases in current through the device.

## ZENER DIODE

#### 10. Explain the construction & working principle of Zener diode.

Explain the Break down mechanisms in semiconductor devices. (May/June 2016), (Nov / Dec 2015) (OR) Explain the Concept of Zener Breakdown and its VI characteristics. (Nov/Dec 2018-R-13)

#### **ZENER DIODE:**

The Zener Diode is a PN junction semiconductor device.

It is fabricated with precise breakdown voltages, by controlling the doping level during manufacturing. Practically, Zener Diodes are operated in reverse biased mode.

Fig.20 Zener Diode

www.EnggTree.com

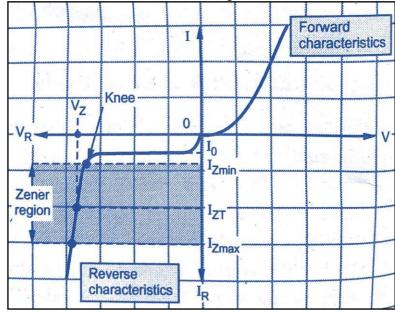

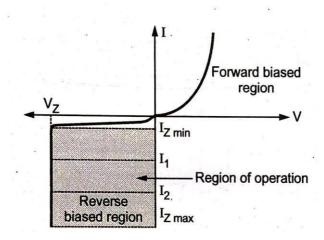

#### **CHARACTERISITCS OF ZENER DIODE:**

#### FORWARD CHARACTERISITCS:

In forward biased condition, the normal rectifier diode and the Zener diode operate in similar fashion. (*Refer: PN diode forward characteristics*)

## Zener reverse characteristics

#### **REVERSE CHARACTERISITCS:**

Zener diode is designed to operate in the reverse biased condition.

In reverse biased condition, the diode carries *reverse saturation current* till the reverse voltage applied is less than the reverse breakdown voltage.

When the reverse voltage exceeds reverse breakdown voltage, the current through it changes drastically but the voltage across it remains almost constant.

Such a breakdown region is a normal operating region for a Zener diode.

The normal operating regions for both diode and Zener are shown in below Fig.

**Fig.** The normal operating region for a rectifier diode and Zener diode

When the applied reverse voltage is increased then, the current through it is very small (few  $\mu A$ ) and it is called Reverse Leakage Current ( $I_o$ )

At certain reverse voltage, the current will increase rapidly. The breakdown occurs and the current at this point (*knee or Zener knee*) is called *Zener knee current* ( $I_{ZK}$  or  $I_{Zmin}$ ).

**Zener knee current** is the minimum Zener current which is must to carry out the operate in Reverse Breakdown Region.

The reverse voltage at which the breakdown occurs is called **Zener Breakdown Voltage or Zener Voltage** ( $V_z$ ). The  $V_z$  is set by controlling the doping level during manufacturing process.

Below the knee, the **reverse breakdown voltage** increases slightly as Zener current  $(I_z)$  increases but, remains almost *CONSTANT*.

The current at which the nominal Zener breakdown voltage is specified is called **Zener Test Current** ( $I_{ZT}$ ).

As the current increases, the power dissipation ( $P_Z = V_Z I_Z$ ) will be increased and if this power dissipation is increased beyond a certain current value, the Zener diode may get damaged. So, there is a maximum current that a Zener diode can carry safely is called **Zener Maximum Current** ( $I_{ZM}$  or  $I_{Zmax}$ ).

In practical circuits, a current limiting resistor is used in series with Zener diode in order to limit the current between  $I_{Zmin}$  to  $I_{Zmax}$ .

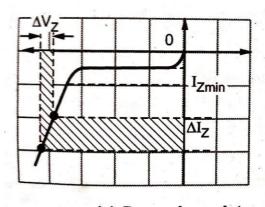

The complete VI characteristics of Zener Diode is shown in Fig.

Fig. VI characteristics of Zener Diode

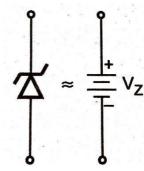

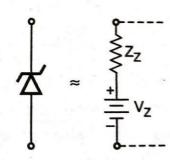

#### **EQUIVALENT CIRCUIT OF ZENER DIODE:**

When the breakdown occurs then  $I_Z$  may increase from  $I_{Zmin}$  to  $I_{Zmax}$  but voltage across Zener remains almost constant. The internal impedance decreases as current increases in Zener region. But this impedance is very small and hence ideally Zener diode is indicated by a battery of voltage  $V_Z$ . This  $V_Z$  remains almost constant in the Zener region which is shown in Fig.

Fig. Ideal equivalent circuit of Zener diode

In practical circuit, the Zener internal resistance is to be considered (even though it is very small) and called as **Zener Dynamic Resistance Zz**. Due to this resistance the Zener region is not exactly vertical, i.e., for the small change in the Zener current  $\Delta I_Z$  produces a small change in Zener voltage  $\Delta V_Z$ . The ratio of  $V_Z$  to  $I_Z$  is called **Zener resistance Zz**.

Hence, the practical Zener diode equivalent circuit should be indicated with a battery of  $V_Z$  along with series resistance  $Z_Z$  as shown in Fig.

Dynamic Resistance,

$$Z_Z = \frac{\Delta V_Z}{\Delta I_Z} = \frac{1}{\left[\frac{\Delta I_Z}{\Delta V_Z}\right]}$$

$Z_Z = \frac{1}{[slope\ of\ the\ reverse\ characteristics\ in\ zener\ region]}$

(b) A.C. equivalent circuit

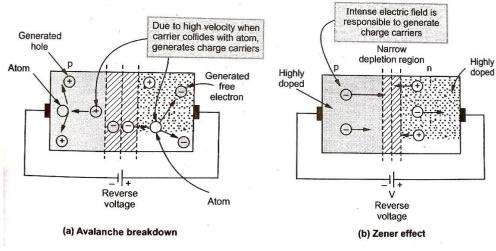

#### **BREAKDOWN MECHANISM IN ZENER DIODE:**

Two distinct breakdown mechanism:

- ✓ Zener Breakdown

- ✓ Avalanche Breakdown

For devices with breakdown voltage *less than 5V - Zener Breakdown*For devices with breakdown voltage *between 5V and 8V - Zener Breakdown and Avalanche Breakdown*For devices with breakdown voltage *above 8V - Avalanche Breakdown*

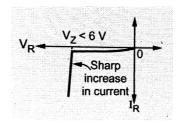

#### ZENER BREAKDOWN:

Zener breakdown occurs at Reverse biased condition because of heavy doping; Practically, **Zener breakdown** is observed in the Zener diodes with breakdown voltage **less than 6V**. In Zener breakdown, the value of the breakdown voltage decreases as PN junction temperature increases, i.e. Negative Temperature Coefficient (NTC)

For applied reverse biased voltage of less than 6V causes a high magnitude electric field (3 X  $10^5$  V/cm) across the depletion region, at the PN junction.

This electric field applies a large force on the valence electron of the atom, tending it to separate them from their respective nuclei. Electron-hole pairs are generated in large numbers and there will be a sudden increase in current. (To limit this current, a current limiting resistor is used in order to protect the Zener diode from being destroyed because of excessive heating at the junction)

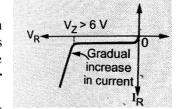

#### **AVALANCHE BREAKDOWN:**

Avalanche Breakdown occurs at Reverse biased condition due to ionization of electron and hole pairs Practically, Avalanche breakdown is observed in the Zener diodes with breakdown voltage greater than 6V. In avalanche breakdown, the value of the breakdown voltage increases as PN junction temperature increases, i.e. Positive Temperature Coefficient (PTC)

For applied reverse biased voltage of greater than 6V causes increased acceleration of minority charge particles. Thus, collision between accelerated charge particles with high velocity and kinetic energy with adjacent atom is involved in breaking the covalent bonds of the crystal structure. This process is called **Carrier Multiplication**.

At this stage, junction is said to be in breakdown and current starts increasing rapidly. To limit this current below  $I_{Zmax}$ , a current limiting resistor is necessary.

Fig. Breakdown Mechanism in Zener Diode

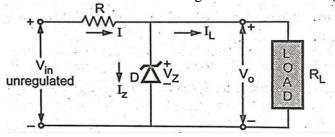

## ZENER AS REGULATOR

## 11. (a) Explain the working of a Zener diode as a regulator? (May 2017) (Nov/Dec 2017) (Nov/Dec 2018 - R17

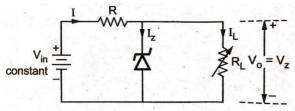

The Zener Diode is used to regulate the *Load Voltage*. Here, the Zener is used in reverse biased condition.

Fig. Zener Diode as a shunt regulator

Under reverse biased condition, the current through the zener diode is very small of the order of few µA, up to certain limit. When enough reverse bias voltage is applied, electrical breakdown occurs and large current flows through the zener diode. The voltage at which the breakdown occurs is called Zener Voltage (Vz).

Fig. VI characteristics of Zener Diode

Under this condition, whatever may be the current, the **voltage** across the Zener is **constant** and **equal to**  $\mathbf{V}_{\mathbf{Z}}$

Since, voltage across the Zener Diode is CONSTANT & equal to Vz, it is connected across the load. :. The Load Voltage (Vo) is equal to Zener Voltage (Vz).

i.e. The Zener Diode acts as an ideal voltage source which maintains a constant load voltage, www.EnggTree.com independent of the current.

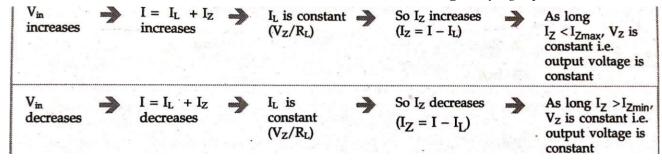

## REGULATION WITH VARYING INPUT VOLTAGE (Line Regulation)

Zener Regulator under varying input voltage condition is shown in Fig.

$$V_0 = V_Z$$

is constant  $I_L = \frac{V_O}{R_L} = \frac{V_Z}{R_L} = constant$

And  $I = I_Z + I_L$

**Fig.** Varying input condition

As long  $I_Z$  is between  $I_{Zmin}$  and  $I_{Zmax}$ , the  $V_Z$  i.e. output voltage  $V_0$  is constant. Thus, the changes in the input voltage is get compensated and output is maintained constant.

The maximum power dissipation for the zener diode is fixed,

$$P_D = V_Z I_{Zmax}$$

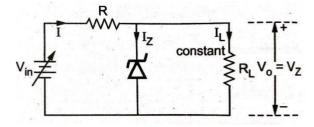

## REGULATION WITH VARYING LOAD (Load Regulation)

Zener Regulator under varying load condition ( $R_L$  is variable) and constant input voltage ( $V_{in}$  is constant) is shown in Fig.

Fig. Varying load condition

$V_o = V_Z$  is constant and  $V_{in}$  is Constant, then for constant R, the current (I) is constant.

As long  $I_Z$  is between  $I_{Zmin}$  and  $I_{Zmax}$ , the  $V_Z$  i.e. output voltage  $V_0$  is constant. Thus, the changes in the load is get compensated and output is maintained constant.

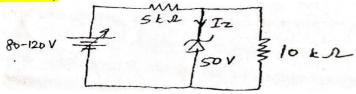

(b) For the following circuit, find the maximum and minimum values of Zener diode current. (Nov/Dec 2018 – R17)

**Solution:**

$$V_{in (min)} = 80V$$

,  $V_{in (max)} = 120V$ ,  $V_Z = 50V$ ,  $R_L = 10K\Omega$ ,  $R = 5K\Omega$

$$I_L = \frac{V_Z}{R_L} = \frac{50}{10 \times 10^3} = 5 \times 10^{-3} = 5mA$$

$$V_{in (min)} = V_Z + IRV_{in (max)} = V_Z + IR$$

$$I = \frac{V_{in\,(\text{min})} - V_Z}{R} \quad I = \frac{V_{in\,(\text{max})} - V_Z}{R}$$

$$I_{(min)} = \frac{80 - 50}{5 \times 10^3} = 6mA \ I_{(max)} = \frac{120 - 50}{5 \times 10^3} = 14mA$$

$$I_{Z(min)} = I_{(min)} - I_{L}$$

$I_{Z(max)} = I_{(max)} - I_{L}$

$$I_{Z (min)} = 6 X 10^{-3} - 5 X 10^{-3} = 1 mA$$

$$I_{Z(max)} = 14 \times 10^{-3} - 5 \times 10^{-3} = 9mA$$

:.  $Minimum\ zener\ current,\ I_{Z(min)}=1mA$

:.  $Maximum\ zener\ current$ ,  $I_{Z(max)} = 9mA$

#### Problems: (Anna University Exam - Solved Problems)

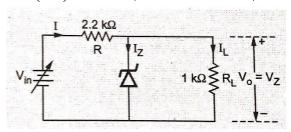

1. For the zener regulator shown in Fig. 5, calculate the range of input voltage for which output will remain constant.

$$I_{Z(min)} = 2.5mA$$

,  $I_{Z(max)} = 25mA$ ,  $V_{Z} = 6.1V$ ,  $r_{Z} = 0 K\Omega$

**Solution:**

$$I_{Z \; (min)} = 2.5 mA$$

,  $I_{Z \; (min)} = 25 mA$ ,  $V_{Z} = 6.1 V$ ,  $r_{Z} = 0 \; K\Omega$ ,  $R = 2.2 \; K\Omega$ ,  $R_{L} = 1 \; K\Omega$

$I_{L} = \frac{V_{Z}}{R_{L}} = \frac{6.1}{1 \; X \; 10^{3}} = 6.1 \; X \; 10^{-3} = 6.1 mA$  (CONSTANT)

$$I_{L} = I_{L} = I_{L$$

$$V_{in\ (min)} = 6.1 + 8.6\ X\ 10^{-3}X\ 2.2\ X\ 10^{-3} = 25.02V$$

$V_{in\ (min)} = 6.1 + 31.1\ X\ 10^{-3}X\ 2.2\ X\ 10^{-3} = 74.52V$   $\therefore V_{in\ (min)} = 25.02V$   $\therefore V_{in\ (max)} = 74.52V$

2. A silicon diode has a saturation current  $7.5\mu$  A at room temperature 300K.Find the saturation current at 400k.  $I_{o1}$ =7.5 x 10-6 A at  $T_1$ =300° K=27° C and  $T_2$ =400 °K=127° C. (Nov/Dec 2016 – R13) Solution: The saturation current at 400°K is

$$I_{02} = I_{01} \times 2^{\frac{\Delta T}{10}} = 7.5 \times 10^{-6} \times 2^{(127-27)/10} = 7.68 \text{mA}$$

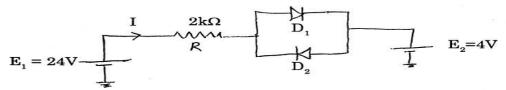

3. Find the current I in the following circuit. (Nov/Dec 2017 – R13)

Assume the diodes to be of silicon and forward resistance of diodes to be zero.

$$I = (E1-E2)/R$$

$I = (24-4)/2000$   $I = 1 \text{ mA}$  Current I is 1mA.

4. An AC voltage of peak value 20V is connected in series with a silicon diode and load resistance of  $500\Omega$ . If the forward resistance of diode is  $10\Omega$  find the peak current through the diode. (Nov/Dec 2018-R17)

Solution:

$$E_m = 20V$$

,  $R_L = 500\Omega$ ,  $R_f = 10\Omega$

$$I_m = \frac{E_m}{R_f + R} \qquad I_m = \frac{20}{500 + 10}$$

$$\therefore I_m = 39.22 \ mA$$

5. (a) Determine the peak output voltage of a half wave rectifier, if the diode has  $V_F =$ 0.7V and the AC input is 22V. (April / May 2019-R17)

**Solution:**

$$V_{po} = V_{pi} - V_F$$

$V_F = 0.7 V,$   $V_{pi} = \sqrt{2}V_i = \sqrt{2} X 22,$   $V_{pi} = 31.1 V$

$V_{po} = 31.1 - 0.7,$   $V_{po} = 30.4 V$

(b) If load resistance is given as  $500\Omega$ , calculate peak output current of the above given half wave rectifier.

Solution:

$$R_L = 500\Omega$$

$I_p = \frac{V_{po}}{R_L} = \frac{30.4}{500}$   $I_p = 60.8 \, mA$  (c) Determine the diode peak reverse voltage (PIV). PIV =  $V_{pi} = 31.1 \, \text{V}$

- (c) Determine the diode peak reverse voltage (PIV).

- 6. What value of series resistor is required to limit the current through a LED to 20 mA with a forward voltage drop of 1.6 V when connected to a 10V supply? (Nov/Dec 2017)

Series resistor,

$$R_S = \frac{V_S - V_D}{I_F}$$

$V_S = 10 \text{ V}; \quad V_D = 1.6 \text{ V}; \quad I_F = 20 \text{ mA} = 20 \times 10^{-3} \text{ A}$

$$R_S = \frac{10 - 1.6}{20 \times 10^{-3}} = 420 \ \Omega$$

- 7. In a semiconductor at room temperature (300°K), the intrinsic carrier concentration and resistivity are 1.5 \* 10<sup>16</sup>/cm<sup>3</sup> and 2 \*10<sup>3</sup>Ω-mrespectively. It is to an extrinsic semiconductor with a doping concentration of 10<sup>20</sup>/cm<sup>3</sup> for the extrinsic semiconductor.

- Calculate (a) Majority carrier concentration, (b) Shift in fermilevel due to doping (c) Minority carrier concentration when its temperature is increased to a value at which the intrinsic concentration 'n<sub>i</sub>' doubles. (NOV/DEC 2012) www.EnggTree.com

Assume the mobility of majority and minority carriers are same and **KT=26 meT** at room temperature.

a) Minority carrier concentration= n<sub>i</sub>

Doping concentration

$$=\frac{(1.5\times10^{16})}{\text{Doping concentration}} = 2.25\times10^{12}\frac{\text{atoms}}{\text{m}^3}$$

We know  $\sigma=nq(\mu_n+\mu_p)$  or  $(\mu_n+\mu_p)=\frac{\sigma}{nq}=\frac{1}{\rho nq}$

$$\frac{1}{2\times10^3)(1.5\times10^{16})(1.6\times10^{-19})}=\frac{1}{4.8}$$

In this case the concentration of majority and minority carriers are same, thus

$$\mu_n + \mu_p = 2\mu_n = \frac{1}{4.8} \text{ or } \mu_n = 0.1042 \frac{m^2}{\text{Volt} - \text{sec}}$$

b) Because of doping concentration>> minority concentration conductivity.

$$\sigma=qn~\mu_n=(1.6\times 10^{-19})(10^{20})(0.10242){=}1.6672$$

Thus resistivity  $R{=}\frac{1}{\sigma}=0.599\Omega cm$

Shift interm level E<sub>F</sub>computed as follows

C)

$$E_A - E_i = KT \log e \frac{n_0}{n_i} = 0.026 \log_e (\frac{10^{20}}{10^{16} \times 15})$$

=0.229<sub>e</sub>V.

Thus E<sub>F</sub> lies0.229<sub>e</sub>V above from fermilevel.

Thus

$$E_F$$

lies  $0.229_eV$  above from fermilevel.

d) Minority carrier concentration =  $\frac{(2\pi i)^2}{\text{doping concentration}} = \frac{[2(1.5\times10^{16})^2]}{10^{20}} = \frac{9\times10^{32}}{10^{20}} = 9\times 10^{12} \text{atoms/cm}^3$ .

#### Additional Questions: PART-A

#### 1. Define valence electron.

Electrons that are in shells close to nucleus are tightly bounced to the atom and have low energy. Whereas electrons that are in shells farther from the nucleus have large energy and less tightly bound to the atom. Electrons with highest energy level exist in the outermost shell of an atom. These electrons determine the electrical and chemical characteristic of each particular type of atom. These electrons are known as valence electrons.

#### 2. What is meant by energy band?

In a single isolated atom, the electron in any orbit possesses define energy. Due to an interaction between atoms the electrons in a particular orbit of one atom have slightly different energy levels from electrons in the same orbit of an adjoining atom. This is due to the fact that no two electrons see exactly the same pattern of surrounding charges. Since there are billions of electrons in any orbit, slightly different energy levels form a cluster or band known as energy band.

#### 3. Define conduction band & valence band.

- o The conduction band is defined as the range of energies possessed by conduction electrons.

- Valence band is defined as the range of energies possessed by valence electros.

#### 4. What are conductors, Insulators and semiconductors?

- A conductor is a material, which easily allows the flow of electric current. The best conductors are copper, silver, gold and aluminum.

- An Insulator is a material that does not conduct electric current. In these materials valence electrons are tightly bound to the atoms.

- O A semiconductor is a material that has an electrical conductivity that lies between conductors and insulators. A semiconductor in it's pure state is neither a good conductor not a good insulator. The most common semiconductors are silicon, Germanium, and carbon.

#### 5. What are the classifications of semiconductors?

Semiconductors are classified as intrinsic and extrinsic semiconductors. A pure semiconductor is called intrinsic semiconductor. A doped semiconductor is called extrinsic semiconductor.

#### 6. What is meant by doping? How the extrinsic semiconductors are classified?

The process of adding impurities to a semiconductor is known as doping.

- o n-type semiconductor

- o p-type semiconductor

#### 7. How a *n*-type semiconductor & p-type semiconductor can be obtained?

- o A n-type semiconductor can be obtained by adding pentavalent impurities to an intrinsic semiconductor. These are atoms with five valence electrons. Typical examples for pentavalent atoms are Arsenic. Phosphorous, Bismuth and Antimony.

- A p-type semiconductor can be obtained by adding trivalent impurities to an intrinsic semiconductor. These are atoms with three valence electrons. Typical examples for trivalent atoms are boron(B), indium (In) and gallium (Ga).

#### 8. Define Fermi level.

Fermi level is the energy at which the probability of occupation by an electron is exactly 0.5.

#### 9. What is the energy band gap of silicon and Germanium at $300^{\circ}K$ ?

For Germanium: 0.66e and for Silicon: 1.12ev

#### 10. What are the different types of voltage regulators?

Based on how regulating element is connected to the load, voltage regulators are classified as

- Series regulator

- Shunt regulator

- Switch-mode regulators or switched mode power supply (SMPS)

#### Additional Ouestions (PART-B)

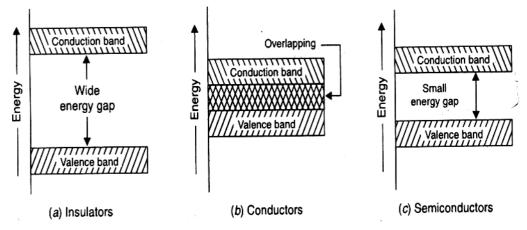

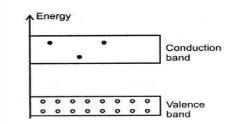

#### 1. Draw and explain the energy band diagram for the following

(i) conductors (ii) Insulators (iii) semiconductors

#### **Insulators:**

The materials in which the condition band and valence bands are separated by a wide energy gap ( $\approx 15$  eV) as shown in figure.

A wide energy gap means that a large amount of energy is required, to free the electrons, by moving them from the valence band into the condition band;

Since at room temperature, the valence electrons of an insulator do not have enough energy to jump in to the condition, therefore insulator do not have an ability to conduct current. Thus insulators have very high resistively (or extremely low conductivity) at room temperatures.

However if the temperature is raised, some of the valence electrons may acquire energy and jump in to the conduction band. It causes the resistively of insulators to decrease. Therefore an insulator have negative temperature co-efficient of resistance.

#### **Conductors:**

The materials in which conduction and valence bands overlap as shown in figure are called conductors. The overlapping indicates a large number of electrons available for conduction. Hence the application of a small amount of voltage results a large amount of current.

#### **Semiconductors:**

The materials, in which the conduction and valence bands are separeated by a small energy gap (1eV) as shown in figure are called semiconductors.

Silicon and germanium are the commonly used semiconductors.

A small energy gap means that a small amount of energy is required to free the elctrons by moving them from the valence band in to the conduction band.

The semiconductors behave like insulators at 0K, because no electrons are available in the conduction band.

If the temperature is further increased, more valence electrons will acquire energy to jump into the conduction band. Thus like insulators, semiconductors also have negative temperature co-efficient of resistance. It means that conductivity of semiconductors increases with the increases temperature.

#### 2. Explain the classification of semi-conducteurs.

#### Classification of semi-conducteurs:-

Semiconductors are classified in to two types

- Intrinsic Semiconductors

- o Exterinsic semi-conducteurs

- > n-type semi-conductor

- > p-type semi-conductor

#### o Intrinsic seiconductor

A semiconductor in an extremely pure form is known as an intrinic semiconductor. An Intrinsic semiconductor, even at room temperature, hole-electron pairs all created. When electric field is applied across an semiconductor intrinisic semiconductor, the current conduction takes place by two process, namely by free electrons and holes.

Free electrons are produced due to the breeding up of fome co-valent bonds by thermal energy. At the same time holes are created in the co-valent bond itself. When electric field is applied across the semi-conducteurs material electrons will move towards the positive terminal of supply, holes will move towards negative terminal of the supply.

Thus current conduction inside this intrinisic semiconductor material is due to movement of holes & electrons.

But the current in the external wire is only because of electrons. Since while applying electric field, holes are attracted towards negative terminal. There one new electron is introduced. This electron will combine with the hole, thus cancelling them.

At the same time electrons are moving towards positive terminal, while leading from this intrinisic material it leaves a hole. Again this holes are attracted towards negative terminal.

#### Extrinisic semiconductor :

The current conduction capability of intrinisic semiconductor is very low at rom temperature. So we can not use it in electric devices.

Hence the current conduction capability must be increased. This can be achieved by adding impurities to the intrinsic semiconductor. So that it become impurity semiconductor (or) Extrinsic semiconductor. The process of adding impurity is known as doping.

The amount & type of impurities have to be closely controlled during the preparation of extrinisic semiconductor. Generally, for  $10^8$  atoms of semiconductor, one impurity atom is added.

The purpose of adding impurity is to increase either the number of free electrons or holes in the semiconductor crystal. If the pentavalent impurity is adding to the semiconductor, a large number of free electrons are produced in the semiconductor.

On the other hand if the trivalent impurtiy is added it introdued large number of holes. Depending upon the type of impurity added, extrisic semiconductors are classified into

- $\triangleright$  n type Semiconductor

- ➤ p type Semiconductor

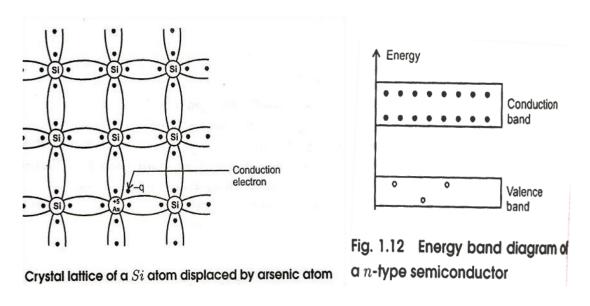

#### n – type Semiconductor:

www.EnggTree.com

**The** number of free electrons in an instrinsic silicon can be increased by adding a pentavalent atom to it. These are atoms with five valence electrons. Typical example for pentavalent atoms are Arsenic, Phosphorous, Bismuth and Antimony.

Four of the pentavalent atoms valence electrons form covalent bond with the valence electrons of Silicon atom, leaving an extra electron. Since valence orbit cannot hold no more than eight electrons the extra electron becomes a conduction electron.

Since the pentavalent atom donnates this extra conduction electron it is often called as a donor atom. For each pentavalent atom added, one free electron exists in a silicon crystal. A small amount of pentavalent impurity is enough to get more number of free electrons is greater than the number of holes this extrinsic semiconductor is known as an n type semiconductor.

When a pentavalent atom is added a number of conduction band electrons are produced. Only a few holes exist in the valence band, created by thermal energy. Therefore in an n-type semiconductor, electrons are majority carriers and holes are minority carriers.

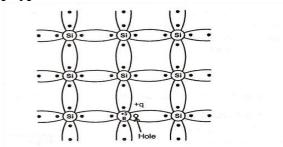

#### p-type semiconductor

Fig. 1.14 Energy band diagram of a p-type semiconductor

Crystal lattice with a Si atom displaced by Boron atom  $\,$   $\,$   $\,$   $\,$   $\,$   $\,$   $\,$   $\,$   $\,$

A p-type semiconductor (p for Positive) is obtained by carrying out a process of <u>doping</u> by adding a certain type of atoms (<u>acceptors</u>) to the <u>semiconductor</u> in order to increase the number of free <u>charge carriers</u> (in this case positive holes).

When the doping material is added, it takes away (accepts) weakly bound outer <u>electrons</u> from the semiconductor atoms. This type of doping agent is also known as an acceptor material and the vacancy left behind by the electron is known as a <u>hole</u>.

The purpose of p-type doping is to create an abundance of holes. In the case of <u>silicon</u>, a trivalent atom (typically from <u>Group 13</u> of the <u>periodic table</u>, such as <u>boron</u> or <u>aluminium</u>) is substituted into the <u>crystal lattice</u>. The result is that one electron is missing from one of the four <u>covalent bonds</u> normal for the silicon lattice. Thus the dopant atom can accept an electron from a neighboring atom's covalent bond to complete the fourth bond. This is why such dopants are called <u>acceptors</u>.

The dopant atom accepts an electron, causing the loss of half of one bond from the neighboring atom and resulting in the formation of a "hole". Each hole is associated with a nearby negatively charged dopant ion, and the semiconductor remains <u>electrically neutral</u> as a whole. However, once each hole has wandered away into the lattice, one proton in the atom at the hole's location will be "exposed" and no longer cancelled by an electron.

This atom will have 3 electrons and 1 hole surrounding a particular nucleus with 4 protons. For this reason a hole behaves as a positive charge. When a sufficiently large number of <u>acceptor</u> atoms are added, the holes greatly outnumber thermal <u>excited</u> electrons. Thus, holes are the <u>majority carriers</u>, while electrons become <u>minority carriers</u> in p-type materials.

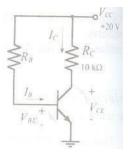

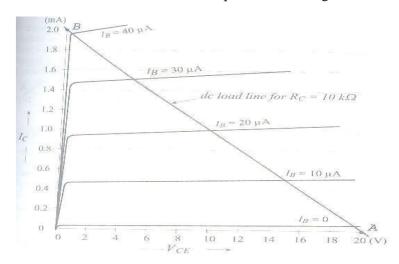

## EnggTree.com EC8353-ELECTRONIC DEVICES AND CIRCUITS

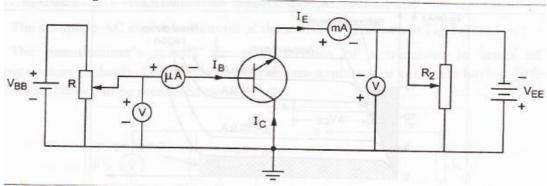

## UNIT-II TRANSISTORS & THYRISTORS PART – A

#### **BJT** (Bipolar Junction Transistor)

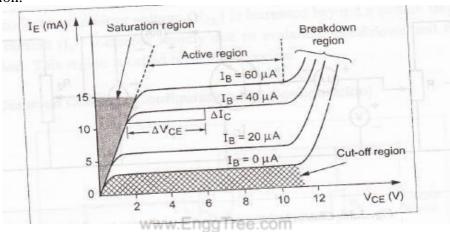

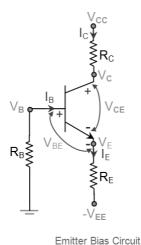

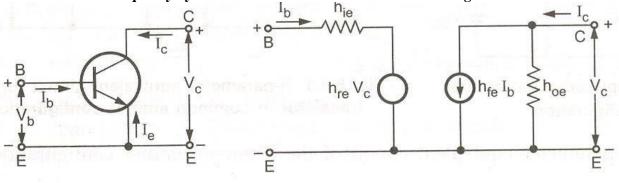

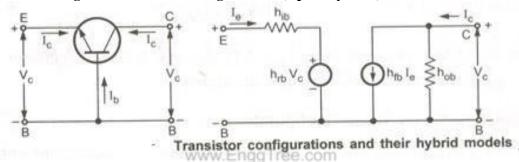

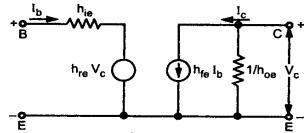

## 1. What is transistor (BJT)? What are the types of circuit connections known as configurations, for operating a transistor?

Transistor (BJT) is a three-terminal device: **Base** (B), **Emitter** (E) & **Collector** (C).

Transistor can be operated in three configurations *Common Base (CB)*, *Common Emitter (CE)* & *Common Collector (CC)*.

According to configuration it can be used for *voltage* as well as *current amplification*.

#### 2. Brief the types of transistors?

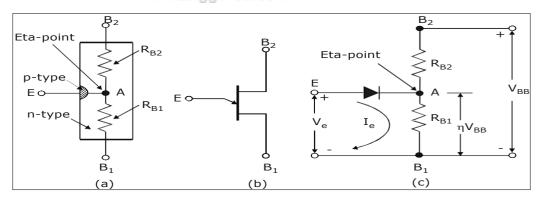

- 1. **UJT** (*Unipolar Junction Transistor*): In unipolar transistor, the current conduction is only due to one type of charge carriers (majority carriers).

- 2. **BJT** (*Bipolar Junction Transistor*): In bipolar transistor, the current conduction is only due to both the types of charge carriers (*Holes and Electrons*).

#### 3. Why an ordinary transistor is called bipolar?

Because the transistor operation is carried out by two types charge carriers (both majority and minority carriers).

#### 4. What are the types of BJT?

Types of BJT:

- 1. NPN

- 2. PNP

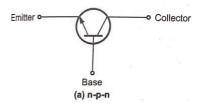

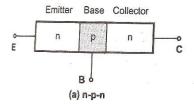

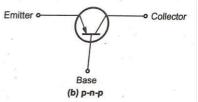

#### 5. Brief the construction of BJT. Draw the symbol and structure and of BJT.

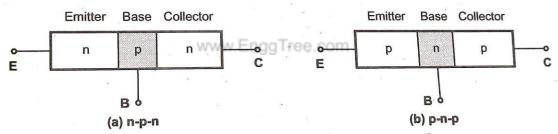

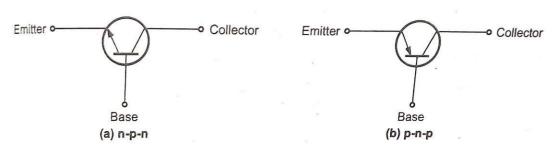

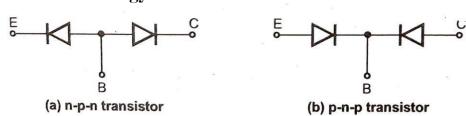

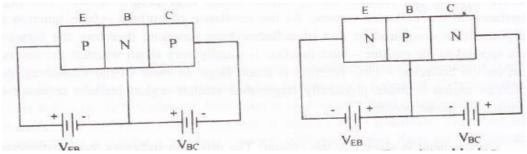

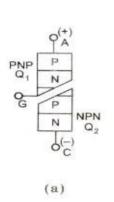

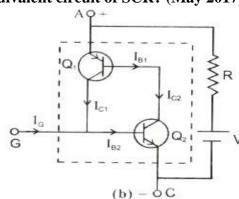

BJT is a three-layer semiconductor device consisting of two PN junctions.

If a layer of P-type material is sandwiched between two layers of N-type the transistor is known as **NPN** transistor.

Fig. Symbol of BJT (NPN type)

Fig. Structure of BJT (NPN type)

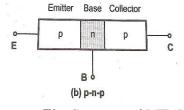

On the other hand, if a layer of N-type material is sandwiched between two layers of P-type, the transistor is known as **PNP transistor**.

Fig. Symbol of BJT (PNP type)

*Fig.* Structure of BJT (PNP type)

#### 6. Why collector is made larger than emitter and base?

Collector is made physically larger than emitter and base because collector is to dissipate much power.

## 7. Why the width of the base region of a transistor is kept very Small as compared to other regions?

Base region of a transistor is kept very small and lightly doped so as to pass most of the injected charge carriers to the collector.

#### 8. How transistor is used as an amplifier? (OR) Explain the word transistor.

The amplification in the transistor is achieved by passing input current signal from a region of low resistance to a region of high resistance.

{This concept of transfer of resistance has given the TRANSfer-resISTOR (TRANSISTOR)}

#### 9. Why silicon is preferred to germanium while manufacturing semiconductor devices?

As the knee voltage of silicon is higher (0.7V) than the knee voltage of germanium (0.3V), silicon will be more stable for temperature variation than germanium.

#### 10. Why transistor (BJT) is called current controlled device?

The output voltage, current or power is controlled by the input current in a transistor. So, it is called the Current Controlled device.

#### 11. State the advantages of a transistor.

- 1. Low operating voltage

- 2. Higher efficiency

- 3. Small size and ruggedness

- 4. 4. Does not require any filament power

# 12. Compare the performance of a transistor in three different configurations. (Nov/Dec 2012) (OR) Compare the input resistance, output resistance and voltage gain of CB, CC and CE configuration. (OR) Compare the performance of CE and CC configuration. (May 2017)

| Property                                     | СВ                          | CE                             | CC                      |

|----------------------------------------------|-----------------------------|--------------------------------|-------------------------|

| Input resistance                             | Low (about $100\Omega$ )    | Moderate (about 750 $\Omega$ ) | High (about 750 kΩ)     |

| Output resistance                            | High (about 450 Ω)          | Moderate (about 45 Ω)          | Low (about $25\Omega$ ) |

| Current gain                                 | 1                           | High                           | High                    |

| Voltage gain                                 | About 150                   | About 500                      | Less than 1             |

| Phase shift                                  | 0 or 360°                   | 180°                           | 0 or 360°               |

| Between input & output voltages Applications | For high frequency circuits | For audio frequency circuits   | For impedance matching  |

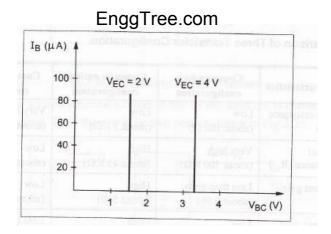

#### 13. Define Early effect? (Nov/Dec 2016)

As the collector voltage  $V_{CC}$  is made to increase the reverse bias, the space charge width between collector and base tends to increase, with the result that the effective width of the base decreases. This known as early effect or base width modulation.

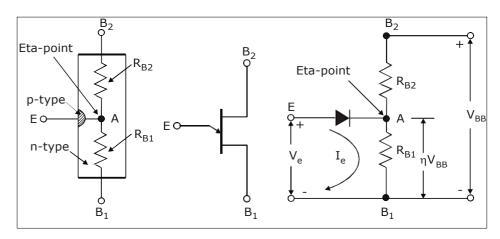

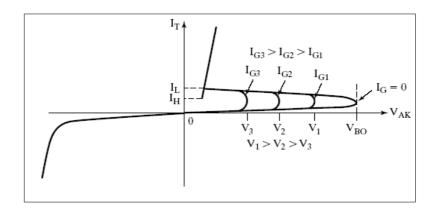

#### 14. What is peak point Voltage?

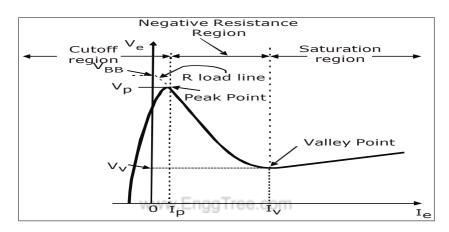

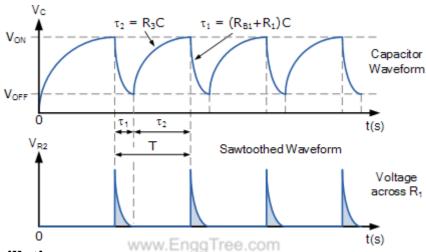

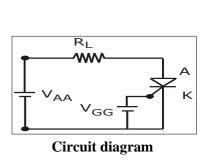

When  $V_{EE}$  exceeds the value  $(V_D + \eta V_{BB})$ , the diode is forward biased and starts to conduct. The value of emitter voltage which makes diode to conduct is called **Peak Point Voltage**.

$$V_p = (V_D + \eta V_{BB})$$

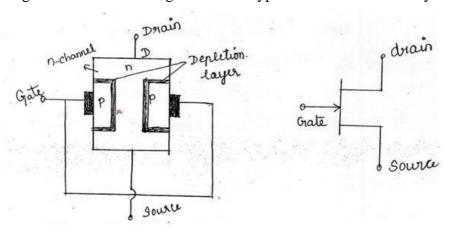

#### JFET (Junction Field EffectnTransistor)

#### 15. What are the different types of FET?

#### **Types of FET:**

- 1. Junction Field Effect Transistor (JFET)

- 2. Metal Oxide Semiconductor Field Effect Transistor (MOSFET)

#### 16. Draw the symbol and structure of JFET.

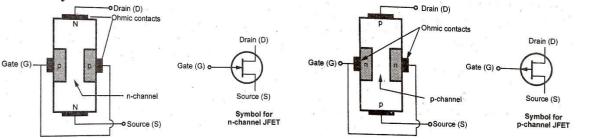

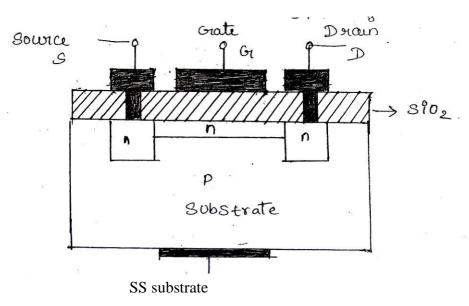

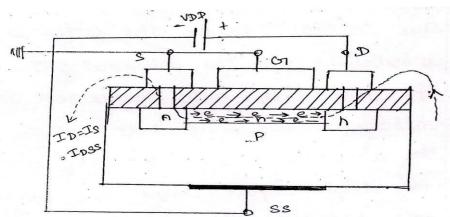

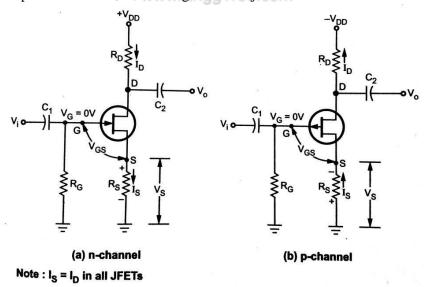

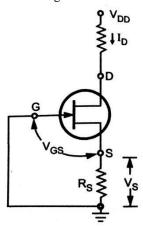

Fig. Structure and for n-channel JFET

Fig. Structure and for p-channel JFET

#### 17. What are the features of JFET?

- a) The operation of JFET depends upon the flow of majority carriers only.

- b) The input impedance of JFET is very high, in the order of  $M\Omega$ .

- c) The JFET is less noisy than BJT.

- d) It exhibits no offset voltage at zero drain current.

- e) It is simple to fabricate.

- F) It occupies less space in an integrated circuit.

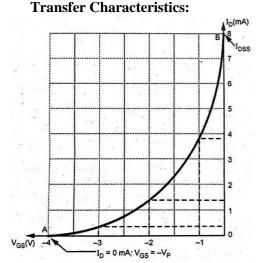

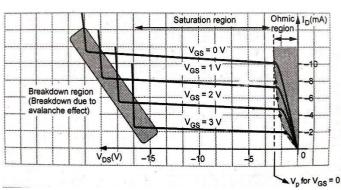

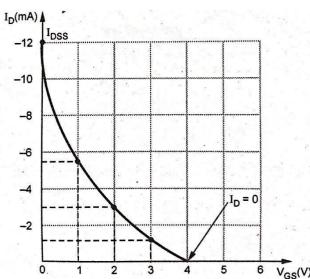

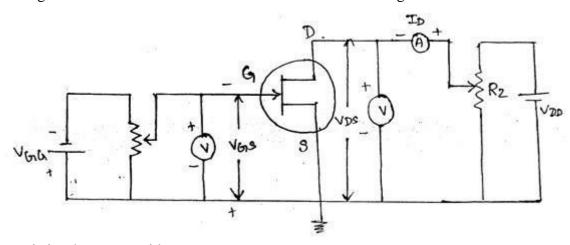

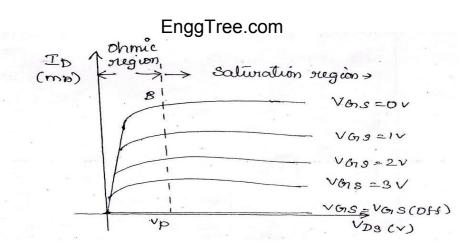

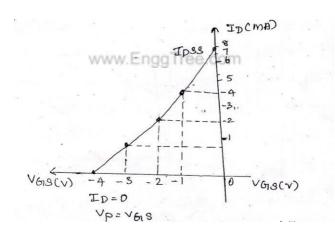

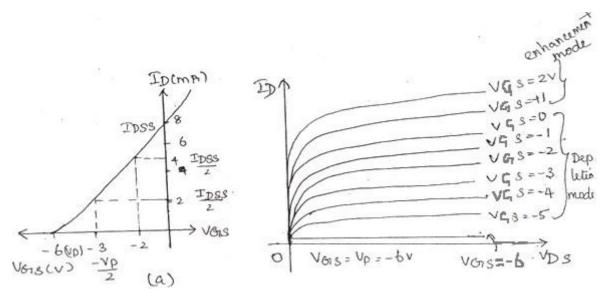

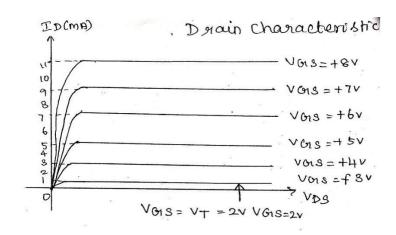

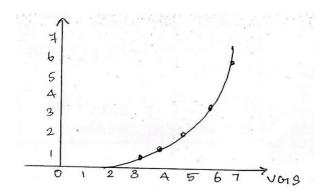

# 18. Draw the transfer and drain characteristics curves of JFET? (May / June 2016)

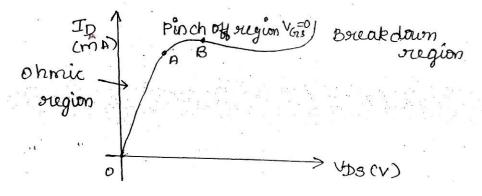

#### **Drain Characteristics:**

Fig. Drain VI characteristics of n-channel JFET

Fig. Transfer characteristics of n-channel JFET

# **Drain Characteristics:**

Fig. Drain VI characteristics of p-channel JFET

# WWW.EnggTreeTransfer Characteristics:

Fig. Transfer characteristics of p-channel JFET

# 19. Define pinch-off voltage of a FET? (Nov/Dec-2012, May/June-2013)

Pinch-off voltage (V<sub>P</sub>) is defined as the drain to source voltage above which drain current becomes almost constant.

# 20. Mention the disadvantages of FET compared to BJT. (Nov/Dec-2012)

Gain bandwidth product of FET is relatively small as compared to BJT.

#### 21. Define drain resistance.

The drain resistance or output  $(r_d)$  is defined as the ratio between change in drain-source voltage  $(V_{DS})$  and change in drain current  $(I_D)$  at constant gate-source voltage  $(V_{GS})$ .

$$r_{\rm d} = \frac{\partial VDS}{\partial i \rho} V$$

# 22. Differentiate FET and BJT (Nov/Dec 2018)

| S.No | FET                                                                                       | ВЈТ                                                            |

|------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1    | Unipolar device (that is current conduction by only one type of either electron or hole). | Bipolar device (current conduction by both electron and hole). |

| 2    | High input impedance due to reverse bias.                                                 | Low input impedance due to forward bias.                       |

| 3    | Gain is characterized by trans conductance                                                | Gain is characterized by voltage gain.                         |

| 4    | Low noise level                                                                           | High noise level                                               |

# 23. What are the applications of JFET?

- a) JFET is used as a buffer in measuring instruments since it has high input impedance and low output impedance.

- b) JFET is used in RF amplifier in FM tuners and communication equipment.

- c) JFET is used in digital circuit's ii computers and memory circuits because of its small size.

- d) It is used oscillators because the frequency drift is low.

# 24. FET has lower thermal noise than BJT - Justify. (April / May 2019-R17)

The FET has high gate-to-main current resistance, on the order of  $100M\Omega$  or more providing a high degree of isolation between control and flow. Because base current noise will increase with shaping time, a FET typically produces less noise than a Bipolar Junction Transistor (BJT).

Thus, found in noise-sensitive electronics such as tuners and low noise amplifiers for VHF and satellite receivers. It is relatively immune to radiation.

# 25. What is the difference between BJT and JFET? (Nov/Dec 2017) (Apr/May 2018) (Nov/Dec 2018-R17)

| S.<br>No. | Bipolar junction transistor (BJT)        | Junction field effect transistor (JFET)         |  |

|-----------|------------------------------------------|-------------------------------------------------|--|

| 1         | Bipolar device (current conduction is by | Unipolar device (current is by only one type of |  |

|           | both electrons and holes)                | carrier-either electrons or holes)              |  |

| 2         | Low input impedance due to forward bias  | High input impedance due to reverse bias        |  |

| 3         | Current control device                   | Voltage control device                          |  |

| 4         | Gain is characterized by voltage gain    | Gain is characterized by Tran conductance.      |  |

| 5         | High noise level                         | Low noise level                                 |  |

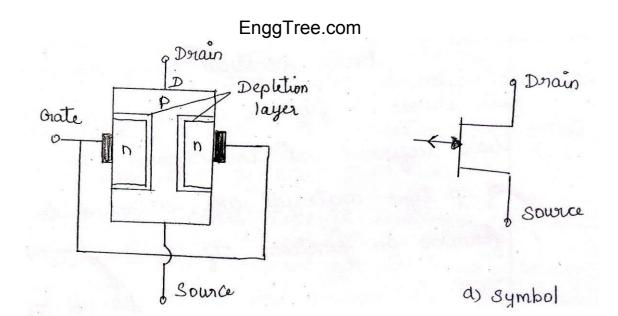

# **MOSFET**

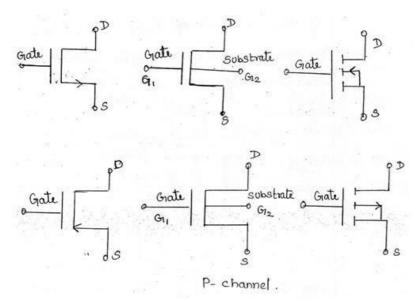

# 26. What are the different types of MOSFET? (May/June-2012, 2013)

The modes of operation of the MOSFET are divided into two types.

- a) Depletion mode MOSFET

- b) Enhancement mode MOSFET

#### 27. What is the other name for MOSFET? (May/June-2012, 2013)

Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is also called as Insulated Gate Field Effect Transistor (IGFET)

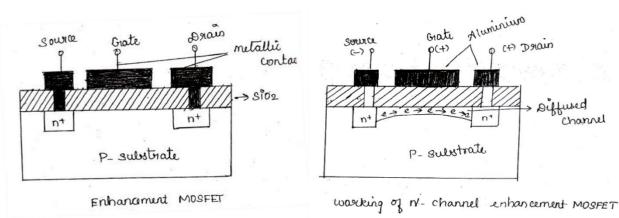

28. If the gate-to-source voltage in an Enhancement MOSFET is zero, what is the current from drain to source?

In an Enhancement MOSFET if the gate-to-source voltage is zero, then the current from drain to source is also zero.

#### 29. What is the major difference in construction of the D-MOSFET and the E-MOSFET?

The depletion MOSFET has a structural channel, whereas the enhancement-MOSFET does not.

#### 30. If the gate-to-source voltage in depletion MOSFET is zero, what is the current from drain to source?

When gate –source voltage is zero for depletion MOSFET, the drain-source current is equal to I<sub>DSS</sub>. (I<sub>D</sub>\_I<sub>DSS</sub>)

#### 31. What are the precautions to be taken when handling MOSFET?

- a) MOSFET should be shipped and stored in a conduction foam rubber.

- b) Prior to soldering, the technician should use a shorting strap to discharge his static electricity.

- c) The soldering iron tip to be grounded. d) MOSFETs should never be inserted into or removed from a circuit with the power on.

- e) The assembler should wear antistatic clothes and ground wrist beads.

- f) All the instruments and metal benches used to test the MOS devices should be connected to ground.

- g) Always avoid touching the device terminals and pick up the transistor by its casing.

#### 32. What are the applications of MOSFET?

- a) It can be used as input amplifiers in oscilloscope, electric voltmeters etc.

- b) It is used in logic circuits.

- c) It is used in computer memories.

- d) It is used in phase shift oscillators.

- e) It is used in FM and TV receivers.

# 33. Depletion MOSFET is commonly known as "Normally-ON" MOSFET why?

The depletion MOSFET can conduct even if the gate to source voltage (V<sub>GS</sub>) is zero. Because of this reason depletion MOSFET is community known as "Normally-ON" MOSFET.

#### 34. What is the difference between JFET and MOSFET? (May / Jun 2016)

| S. No. | JFET                                                                     | MOSFET                                                           |

|--------|--------------------------------------------------------------------------|------------------------------------------------------------------|

| 1      | Reverse bias for gate                                                    | Positive or negative gate voltage                                |